# **PIL-IO** board notes

For use with firmware 2.x

J-F Garnier, Feb. 2016

General Description

PIL-IO Board Description and Setup PIL-IO board kit PCB layout and bill of material Additional wiring PIL-IO supply and I/O connectors HP-IL cable wiring PIL-IO board basic test

PIL-IO Board Usage PILPIO1 device PILSER1 device

PIL-IO firmware history Firmware versions

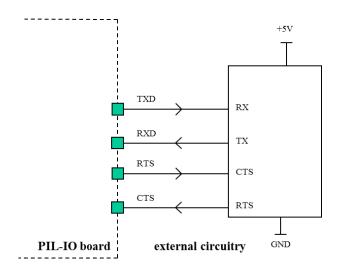

Serial handshake mode

# **1. General Description:**

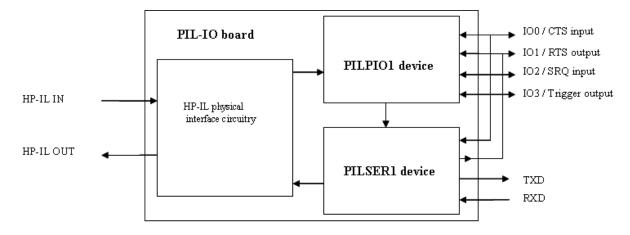

The PIL-IO board provides 4 digital input/output lines and a serial link to the HP-IL loop. It can be driven by any HP-IL controller such as the HP-41C or the HP-71B. The PIL-IO board is intended to be used by electronic hobbyists.

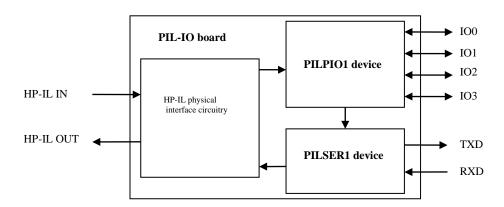

The PIL-IO board provides 2 HP-IL device functions at the same time:

- a mini HP-IL/GPIO interface with 4 I/O lines,

- a mini HP-IL/serial interface with logic level Rx and Tx lines.

The 4 I/O lines can be used either as inputs or outputs in any combination. The serial Tx and Rx lines can be used to interface with another microcontroller using an asynchronous serial communication link (UART). All the I/O and Rx/Tx lines are 5V logic (TTL/CMOS compatible logic) The power supply is not included. A 5V supply has to be provided by the user to the board.

The PIL-IO will work with any HP-IL controller such as the HP-41C, HP-71B or HP-75C.

With the HP-41C, OUTA is used to set the 4 I/O lines, by sending a hexa-coded character that is the binary value corresponding to lines 0-3:

For instance "0" OUTA clears all lines 0 to 3,

"2" OUTA sets line 1, and clears lines 0, 2, 3.

INSTAT reads the status of the I/O lines, the result is in flags 0 to 3 and decimal value in X.

With the HP71, the equivalent commands are: OUTPUT :1,"0" clears all lines 0 to 3, OUTPUT :1,"2" sets line 1, and clears lines 0, 2, 3. X=SPOLL(1) read the status of the I/O lines, the result is in the variable X

This document gives the necessary information to connect the board and use it with a HP-41C or HP-71B and their respective HP-IL module.

# 2. PIL-IO Board Description and Setup

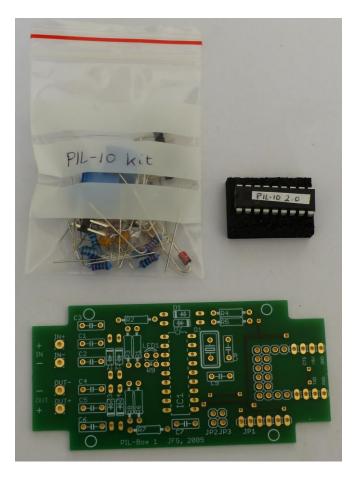

# PIL-IO board kit

- 1 PCB

\_

- 1 programmed microcontroller PIC 16F1826

- 1 component set:

- o R1..R9

- o C1..C7

- o D1, D2

- o Z1, Z2, Z3, Z4

- o LED

- o Zener diode BZX85 5.6V

- o capacitor 4.7uF 25V

- $\circ$  18 pts socket for the uC

- connectors for HP-IL cable (2) with wire terminals (4)

- o I/O connectors: JP1 6pts , JP2/JP3 2 pts

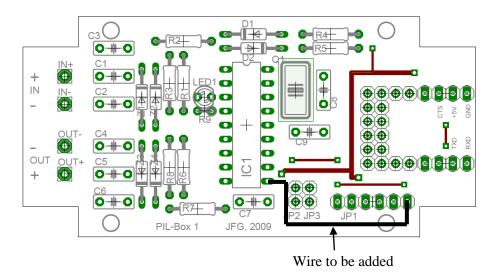

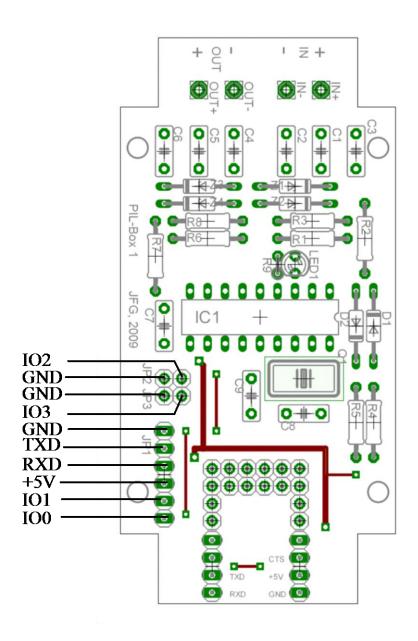

# **PCB** layout:

# **Bill of Material:**

| R1, R2:       | 220 Ohms                                                   |

|---------------|------------------------------------------------------------|

| R3:           | 10 kOhms                                                   |

| R4, R5:       | 22 kOhms                                                   |

| R6, R7, R8:   | 150 Ohms                                                   |

| R9:           | 470 Ohms – vertical mounting, used only if LED1 is mounted |

| C1, C2, C4, C | C5: 22 nF                                                  |

| C3, C7:       | 100 nF                                                     |

| C6:           | 100 pF                                                     |

| D1, D2:       | 1N4148                                                     |

| Z1, Z2, Z3, Z | 4: BZX55-5.1V                                              |

| LED1:         | 3mm LED (optional) – cathode (shortest lead) towards IC1   |

| IC1:          | Microchip 16F1826 (on socket)                              |

|               |                                                            |

Note that the capacitors C8, C9 and the crystal Q1 are no more used with the 16F1826 uC.

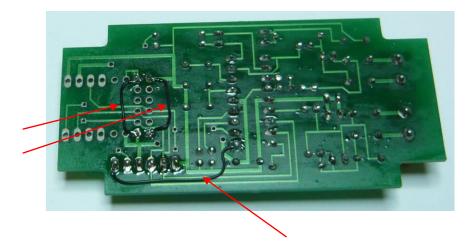

# Additional wiring for the PIL-IO board:

A wire is need between IC1, pin 10 and JP1, pin 6 (see above).

It is recommended to mount a 4.7 to 10uF capacitor (16V min) and a 5.6V Zener diode (BZX85 5.6V) on the supply lines on the board, for proper decoupling and protection against incorrect voltage or polarity.

Below is the suggested wiring for these 2 components:

# **PIL-IO supply and I/O connectors:**

# **HP-IL cable wiring:**

The IN and OUT cables must be wired like this:

See the original PIL-Box setup document for more details.

# **PIL-IO board basic test:**

Apply a 5V supply to the PIL-IO board. The LED should blink 3 times. If yes, the uC is working correctly.

Connect a HP-41C or HP71B to the PIL-IO:

- HP-41C:

- do "PILPIO1" FINDID.

If the result is 1, then the PIL-IO board is working correctly and the HP-IL cables are correctly wired.

HP-71B: do RESTORE IO, then DEVADDR("PILPIO1") If the result is 1, then the PIL-IO board is working correctly and the HP-IL cables are correctly wired.

# 3. PIL-IO Board Usage

The PIL-IO board provides 2 HP-IL device functions at the same time: - "PILPIO1": a mini HP-IL/GPIO interface with 4 I/O lines,

- "PILSER1": a mini HP-IL/serial interface with logic level Rx and Tx lines.

# **PILPIO1 device:**

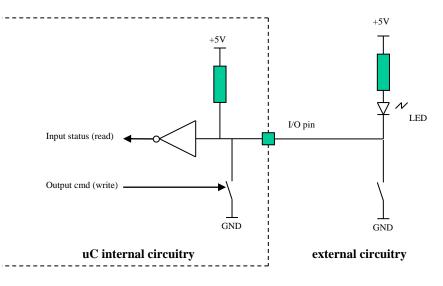

The 4 I/O lines IO0 to IO3 are used for both input and output. No special configuration is needed. The I/O structure is like this:

Writing a '1' to the output drives the I/O low (closed to ground). An external load connected between the I/O pin and the +5V (such as a LED as indicated) is activated.

Writing a '0' to the output drives the I/O high (pulled up by the internal resistor). The LED is off.

The output drive capability is up to 8 mA when the I/O is driven low.

The internal pullup resistor provides about 100 uA.

To use an I/O as an input, write '0' to the output. With no external signal applied on the I/O pin, the status is 0. If the I/O line is driven low (for instance by an external switch as indicated), then the status is 1.

The inputs are TTL compatible.

See the electrical specification of the PIC16F1826 uC on next page for more details.

| Sym. | Characteristic                            | Min.             | Typ† | Max.     | Units | Conditions                                                              |  |

|------|-------------------------------------------|------------------|------|----------|-------|-------------------------------------------------------------------------|--|

| VIL  | Input Low Voltage                         |                  |      |          |       |                                                                         |  |

|      | I/O PORT:                                 |                  |      |          |       |                                                                         |  |

|      | with TTL buffer                           | —                | —    | 0.8      | V     | $4.5V \le VDD \le 5.5V$                                                 |  |

|      |                                           | —                | _    | 0.15 VDD | V     | $1.8V \le VDD \le 4.5V$                                                 |  |

|      | with Schmitt Trigger buffer               | —                | -    | 0.2 Vdd  | V     | $2.0V \le VDD \le 5.5V$                                                 |  |

|      | with I <sup>2</sup> C™ levels             | _                | _    | 0.3 VDD  | V     |                                                                         |  |

|      | with SMBus™ levels                        | _                | _    | 0.8      | V     | $2.7V \le VDD \le 5.5V$                                                 |  |

|      | MCLR, OSC1 (RC mode)(1)                   | _                | _    | 0.2 Vdd  | V     |                                                                         |  |

|      | OSC1 (HS mode)                            | _                | _    | 0.3 VDD  | V     |                                                                         |  |

| Vih  | Input High Voltage                        |                  |      |          |       |                                                                         |  |

|      | I/O ports:                                |                  | _    | _        |       |                                                                         |  |

|      | with TTL buffer                           | 2.0              | _    | —        | V     | $4.5V \le VDD \le 5.5V$                                                 |  |

|      |                                           | 0.25 VDD+<br>0.8 | —    | —        | V     | $1.8V \le VDD \le 4.5V$                                                 |  |

|      | with Schmitt Trigger buffer               | 0.8 VDD          | _    | —        | V     | $2.0V \le VDD \le 5.5V$                                                 |  |

|      | with I <sup>2</sup> C <sup>™</sup> levels | 0.7 VDD          | _    | _        | V     |                                                                         |  |

|      | with SMBus™ levels                        | 2.1              | _    | _        | V     | $2.7V \le VDD \le 5.5V$                                                 |  |

|      | MCLR                                      | 0.8 VDD          | _    | _        | V     |                                                                         |  |

|      | OSC1 (HS mode)                            | 0.7 VDD          | _    | _        | V     |                                                                         |  |

|      | OSC1 (RC mode)                            | 0.9 VDD          | _    | _        | V     | (Note 1)                                                                |  |

| lil  | Input Leakage Current <sup>(2)</sup>      |                  |      |          |       |                                                                         |  |

|      | I/O ports                                 |                  | ±5   | ± 100    | nA    | Vss $\leq$ VPIN $\leq$ VDD, Pin at high-<br>impedance at 85°C           |  |

|      |                                           |                  | ± 5  | ± 1000   | nA    | 125°C                                                                   |  |

|      | MCLR <sup>(3)</sup>                       | —                | ± 50 | ± 200    | nA    | Vss ≤ VPIN ≤ Vpp at 85°C                                                |  |

| IPUR | Weak Pull-up Current                      |                  |      |          |       |                                                                         |  |

|      |                                           | 25               | 100  | 200      |       | VDD = 3.3V, VPIN = VSS                                                  |  |

|      |                                           | 25               | 140  | 300      | μA    | VDD = 5.0V, VPIN = VSS                                                  |  |

| Vol  | Output Low Voltage <sup>(4)</sup>         |                  |      |          |       |                                                                         |  |

|      | I/O ports                                 |                  |      |          |       | IOL = 8mA, VDD = 5V                                                     |  |

|      |                                           |                  | —    | 0.6      | V     | IOL = 6mA, VDD = 3.3V                                                   |  |

| Vou  | Output Lligh Voltage(4)                   |                  |      |          |       | IOL = 1.8mA, VDD = 1.8V                                                 |  |

| Vон  | Output High Voltage <sup>(4)</sup>        |                  |      |          |       |                                                                         |  |

|      | I/O ports                                 | Vdd - 0.7        | —    | _        | v     | Іон = 3.5mA, VDD = 5V<br>Іон = 3mA, VDD = 3.3V<br>Іон = 1mA, VDD = 1.8V |  |

PIC16F1826 I/O specification.

| IO0 | I01 | IO2 | IO3 | Decimal | Hexa char.   |

|-----|-----|-----|-----|---------|--------------|

| 0   | 0   | 0   | 0   | 0       | "0"          |

| 1   | 0   | 0   | 0   | 1       | "1"          |

| 0   | 1   | 0   | 0   | 2       | "2"          |

| 1   | 1   | 0   | 0   | 3       | "3"          |

| 0   | 0   | 1   | 0   | 4       | "4"          |

| 1   | 0   | 1   | 0   | 5       | "5"          |

| 0   | 1   | 1   | 0   | 6       | "6"          |

| 1   | 1   | 1   | 0   | 7       | "7"          |

| 0   | 0   | 0   | 1   | 8       | "8"          |

| 1   | 0   | 0   | 1   | 9       | <b>''9''</b> |

| 0   | 1   | 0   | 1   | 10      | "A"          |

| 1   | 1   | 0   | 1   | 11      | "B"          |

| 0   | 0   | 1   | 1   | 12      | "C"          |

| 1   | 0   | 1   | 1   | 13      | "D"          |

| 0   | 1   | 1   | 1   | 14      | "E"          |

| 1   | 1   | 1   | 1   | 15      | "F"          |

#### I/O state, decimal values read for input, hexa character to be written for output:

#### **Programming examples with the HP-41C:**

LBL "IOEX1" "PILPIO1" FINDID SELECT 10 LBL 01 "1" OUTA "2" OUTA "4" OUTA "4" OUTA "8" OUTA "0" OUTA DSE X GTO 01 This example successively drives the 4 lines IO0 to IO3 low 10 times.

LBL "IOEX2" "PILPIO1" FINDID SELECT "0" OUTA LBL 01 INSTAT VIEW X GTO 01 This example continuously reads the I/O status and displays it in flags 0-3 and as a decimal value in X.

#### With the Extended I/O module HP82183A:

CLRDEV or CLRLOOP: drives all the I/O line to 0 (open). ID: returns "PILPIO1D". The 'D' character indicates the firmware revision. AID: returns 64. 64 FINDAID: finds the PILPIO1 address.

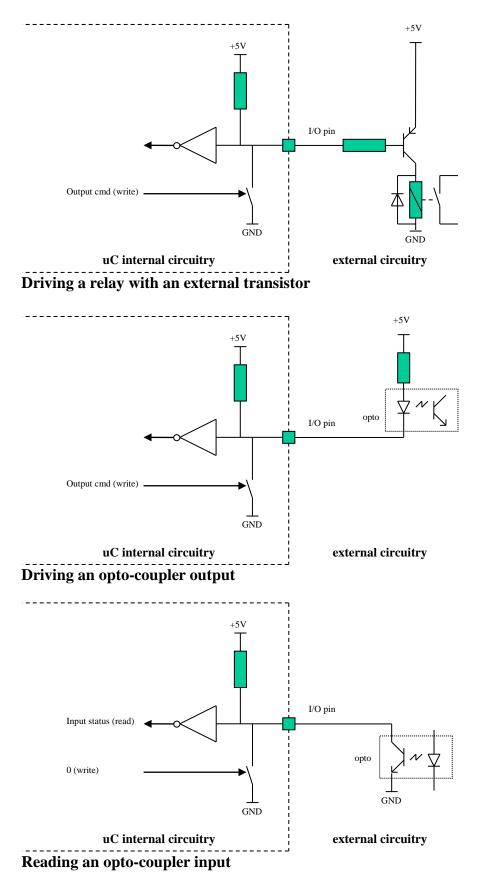

# **Application examples:**

## **PILSER1 device:**

The TXD and RXD serial lines are logic +5V CMOS signals, coming from the USART of the PIC16F1826 uC. They are NOT at RS232 level.

The primary function of the serial lines is to interface with an external microcontroller to extend the functionalities of the PIL-IO.

#### The USART is programmed as: 9600 bps, 8 bits, 1 start, 1 stop, no parity.

No software handshake is provided. A hardware handshake mode is available on firmware revision 1.2 and higher, see the section below on firmware revision for details. There is a 64 bytes input buffer.

A status byte is available. It can be read by the HP-IL controller to get the status of the serial communications (HP-41C: INSTAT function, HP-71B: SPOLL function).

#### **Status byte format:**

| Bit | Value | Description                                                            |  |  |  |

|-----|-------|------------------------------------------------------------------------|--|--|--|

| 0   | 1     | Data available in the receive buffer. Cleared when buffer is empty     |  |  |  |

| 1   | 2     | Line-feed (10 decimal) received. Cleared after reading the status byte |  |  |  |

| 2   | 4     | IO0 / CTS input (firmware 1.2 and higher)                              |  |  |  |

| 3   | 8     | Buffer overflow. Cleared after reading the status byte                 |  |  |  |

| 4   | 16    | Framing error. Cleared after reading the status byte                   |  |  |  |

| 5   | 32    | (unused)                                                               |  |  |  |

| 6   | 64    | IO2 / Service Request input (firmware 1.2 and higher)                  |  |  |  |

Bit 0 can be used to check if there is some data in the received buffer.

Bit 1 can be used to check if a complete line ending with LF has been received

Bits 3 and 4 are for error checking. Bit 3 is set if more than 64 bytes are received. Bit 4 is set if a character is not correctly received (for instance no stop bit detected), usually meaning that the transmission rate is not consistent between transmitter and receiver.

Bits 2 and 6 (firmware 1.2 and higher) indicate the status of the IO0/CTS and IO2/SRQ inputs.

#### **Programming example with the HP-41C:**

LBL "IOEX3" "PILSER1" FINDID SELECT INSTAT INA "ABCDEF" OUTA INSTAT INA

This example reads the status byte and input buffer to clear any previous state, sends the string "ABCDEF", then reads the status byte and the input buffer.

If the RXD and TXD lines are connected together (local loopback), then the flags 0 and 1 will be set and the ALPHA register will hold "ABCDEF".

### With the Extended I/O module HP82183A:

CLRDEV or CLRLOOP: clears the input buffer and status byte. ID: returns "PILSER1D". The 'D' character indicates the firmware revision. AID: returns 66. 66 FINDAID: finds the PILSER1 address. The INAN, OUTAN, etc variants can be used for advanced communication management.

### Note:

If the serial lines are not used, it is recommended not leave the RXD line unconnected, for instance put a jumper between RXD and TXD on the connector JP1.

# **Application examples:**

Connection between the PIL-IO and an external circuitry (default configuration).

Connection between the PIL-IO and an external circuitry (optional handshake mode configuration - firmware 1.2 and higher).

# 4. PIL-IO firmware history

The firmware 1.x are using a PIC16F628A uC. The firmware 2.x are now using a PIC16F1826 uC.

## **Firmware versions:**

Version 1.0:

- Initial version.

- HP-IL Devices IDs: PILPIO1A, PILSER1A.

Version 1.1:

- Brownout removed to be compatible with a power supply using 3 AA/AAA batteries.

- Addition of a power down mode: when receiving a HP-IL Loop Power-down command (LPD frame), the PIL-IO goes to sleep mode with a power consumption reduced from 3mA to 0.2 mA (typ). The state of the I/O lines is preserved. No character can be received from the serial line in sleep mode.

Addition of the trigger function: when receiving a HP-IL Trigger command (GET frame), the line IO3 is pulsed down for 800 us, unless IO3 is already driven low. This provides a certain level of compatibility with HP82166 applications that were using the trigger line.

HP-IL Devices IDs: PILPIO1B, PILSER1B.

Version 1.2:

- Addition of a mode with serial receive/transit handshake signals and Service Request capability (SRQ bit in HP-IL frames). The handshake lines are using the IO0 and IO1 lines and the SRQ input is using the IO2 line. This mode is entered by sending a HP-IL Goto Local command (GTL frame) to the PILSER1 device, and is exit by sending a Goto Local command to the PILPIO1 device. See detailed description below.

- Addition of a 16-byte output buffer to optimize the data transfer in handshake mode.

- HP-IL Devices IDs: PILPIO1C, PILSER1C.

Version 2.0:

- Same features than version 1.2, but using a 16F1826 uC.

- HP-IL Devices IDs: PILPIO1D, PILSER1D.

# Serial handshake mode with CTS/RTS lines and Service Request input (firmware version 1.2 and later):

When a HP-IL Goto Local command (GTL frame) is sent to the PILSER1 device, the IO0-IO3 lines are normally no more available to the PILPIO1 device but are assigned to serial handshake functions for the PILSER1 device.

A HP-IL Goto Local command sent to the PILPIO1 device gives the control of the IO0-IO3 lines back to the PILPIO1 device.

In serial handshake mode, the IO0 and IO1 lines are used as handshake lines:

- IO0 is the CTS input: character transmission is enabled only if CTS is active (low level), - IO1 is the RTS output: when there is less than 48 characters in the input buffer, the RTS output signal is active (low level) to indicate that the PILSER1 device is ready to accept characters. When the input buffer is nearly full (more than 56 characters), the RTS line is driven false (high level).

The IO2 line is the SRQ input: when the SRQ line is driven low, a HP-IL Service Request is indicated on each data and identify frames (DSR or ISR frames).

The CTS (IO0) and SRQ (IO2) states are indicated in the PILSER1 status byte in bits 2 and 6 respectively, regardless of the normal I/O or serial handshake mode.

The HP-IL Goto Local command (GTL frame) is sent by the HP-IL LOCAL function of the HP-41C / HP-71B / HP-75C/D.

The HP-IL REMOTE command disables the access to the serial data buffers, and should not be used.

# I/O lines functions:

| Lines | Normal I/O mode                    | Serial handshake mode  | Serial status bit |  |

|-------|------------------------------------|------------------------|-------------------|--|

|       | (default, or after GTL to PILPIO1) | (after GTL to PILSER1) |                   |  |

| IO0   | general purpose I/O                | Serial CTS input       | 2                 |  |

| IO1   | general purpose I/O                | Serial RTS output      | -                 |  |

| IO2   | general purpose I/O                | Service Request input  | 6                 |  |

| IO3   | general purpose I/O / Trigger      | Trigger output         | -                 |  |

|       | output                             |                        |                   |  |