# How fast is HP-IL?

A discussion of the HP-IL performance, from specifications to real measurements.

PIL-Box optimization.

### How fast is HP-IL: what marketing said.

- HP "Marketing" often presented the HP-IL as able to reach a maximum speed of **20 kBytes/s**, much faster than the standard RS232 link of the time (~1 kByte/s at 9600 bps).

- ■This was based on the ~50us HP-IL frame duration (one byte transmission time), but has nothing to do with operation in real conditions.

- This figure have been used more or less unchanged by several reviews on HP-IL:

HPIL is suited to CMOS, battery-powered instruments. HPIL devices transmit data serially in a loop at up to 20 kBytes/sec.

From Digital Design, June 1982

### **Data Transfer Rates**

The rate at which data may be transferred over the loop interface is theoretically limited to 20K (20,000) bytes per second. Using equipment currently available (at the time of this printing), speeds of about 2K bytes per second are achievable. This translates to about half of a page of text (on an  $8\frac{1}{2}^{n} \times 11^{n}$  piece of paper) per second.

From "The HP-IL system: An Introduction Guide", Kane, Harper & Ushijima, 1982, p.6

#### µP-PERIPHERAL CHIPS INTERFACES

. .

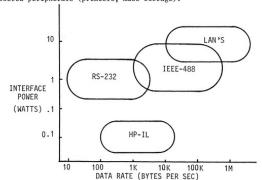

Figure 5.15 shows a comparison among the HP-IL interface and other well known interfaces in a speed vs power requiments graph 14. As it can be seen HP-IL is faster than RS-232 and slower than HFIB. However, it is unique in its low power requirements. It is this combination of good speed with very low power that makes HP-IL a suitable interface for portable devices. The most obvious is the portable computer needing battery powered peripherals (printers, mass storage).

Figure 5.15. HP-IL speed/power comparison.(After Ref. 14).

From "Interface Fundamentals in Microprocessor-Controlled Systems", Chris Georgopoulos, 1985

## How fast is HP-IL: a better analysis (HP)

- The HP Journal on HP-IL (January 1983) provided a much better analysis:

- Max theoretical performance with the 1LB3 HP-IL chip (software delays not included):

1 device: 7.1 kB/s 3 devices: 6.4 kB /s 5 devices: 5.5 kB/s

Real performances with actual controllers:

HP-85: 3 kB/s

HP-41C: 200 Bytes/s

(The HP-75C was not mentioned, and the HP-71B was not yet existing)

#### How Fast Is the HP-IL?

Determining the data rate for an interface is often difficult and misleading since it is usually dependent on highly variable hardware and software delays in the devices connected to the interface, rather than the maximum specifications of the interface itself. For any statement of data rate to be at all useful, the conditions under which the measurement is made must be carefully and completely specified.

The first important question is, "How tast could the HP-IL be if the devices did not limit the speed?" Assume a loop with only two devices: a controller/talker and a listener. The talker is continuously sending data frames to the listener. Because the first frame bit determines whether or not a frame is a data frame (as opposed to a command or ready frame), the listener will immediately retransmit the frame after only a one-bit delay and simultaneously load the frame into its buffer. Similarly, the talker can begin framsmitting its next data frame after receiving only the first bit of the previous data frame. Error checking of the received frame is either not done or is done in parallel with transmission of the following frame.

Under these conditions, a continuous stream of data would fill the loop, limited only by the HP-IL timing specifications. These specifications say that a frame can be sent every 49 µs. The maximum data rate that could possibly be achieved is then slightly more than 20 kilobytes per second (each frame contains one byte of data). Furthermore, the loop could contain as many as ten of these "no-extra-delay" devices before the data rate would begin to suffer.

While such devices could certainly be built with existing technology, the HP-IL interface integrated circuit (see article on page 16) trades off this maximum performance for somewhat lower cost. This leads immediately to the next important question. "How fast would the HP-IL be if it were limited only by the existing interface IC and not by any added software delays?" Once again, the two-device loop example is useful, except that the devices now use the real HP-IL interface IC as opposed to a hypothetical one.

The sequence of events would proceed more or less as follows. After the data byte is written to the talker's HP-IL, chip, there is a  $4+\mu s$  delay before transmission of the bits starts. The frame takes  $46\,\mu s$  to be sent, and then the listener delays  $7\,\mu s$  before passing the byte to its microprocessor. The listener now retransmits the frame, which again has a  $4+\mu s$  delay followed by a  $46+\mu s$  transmit time. After the frame is received at the talker, there is a final  $34+\mu s$  wait while error-checking is done before the following frame can be seen the same services of the same services.

The grand total is 141 microseconds per frame, which translates to just over 7 kilobytes per second. Because the active

listener does not retransmit the frame before it has been completely received, any additional devices will add to the time and degrade the data rate somewhat. An idle device using the present HP-IL interface IC delays a data frame by 13  $\mu$ s so that three devices on the loop will reduce the speed to about 6.4 kilobytes per second, four devices will only support 5.9 kilobytes per second, and five will run at 5.5 kilobytes per second.

As the analysis gets closer and closer to the real world, software delays must also be accounted for. With a reasonably fast microprocessor and time-efficient (not necessarily ROM-efficient) code, an extra delay of no more trian 50  $\mu$ s could probably be achieved in each active HP-IL device. At a little less than 250  $\mu$ s per frame, the two-device loop would have a speed of just over 4 kilobytes per second, three devices would operate at 3.8 kilobytes per second, four at 3.6, and five at 3.5.

Probably the easiest way to determine the data rate of a real system is simply to total the delay times of the individual devices involved. These times must be measured from the end of the received frame to the end of the frame transmitted through the device. Naturally, this value will vary somewhat depending on whether the device is acting as a talker or a listener and what type of data is being transmitted, but an average value is still useful.

For the HP-IL interface integrated circuit without extra software delays, the delay is around 70  $\mu s$ . When the assumed software delay is added, the number goes to 120  $\mu s$ . An HP-85 Personal Computer with the I/O ROM and HP-IL interface can achieve a frame delay of roughly 300  $\mu s$ . The HP 82161A Digital Cassetts Drive takes 600  $\mu s$  per frame for a transfer of less than one 256-byte record, but increases to an average of 2600  $\mu s$  per frame for very large blocks of data because of the record gaps on the tape. The slowest device is the HP-41C Programmable Calculator with its bit-serial microprocessor at about 5000- $\mu s$  delay per frame.

A little computation then indicates that the combination of the HP.41C and the cassette drive can achieve a data rate of 175 bytes per second for short transfers and about 130 bytes per second for longer blocks of data. An HP.41C talking to an HP.85 can run at a little less than 190 bytes per second. If a cassette drive were used with an HP.85, the rate would be 350 bytes per second for long transfers, and about 1100 bytes per second for short ones. Two HP.85 Computers could communicate with each other at a little less than 1700 bytes per second across the HP-IL.

Clearly, the HP-IL is fairly slow when compared with the HP-IB. However, the data rate and other features of this interface system are well suited to the primary area of intended application. lowcost, battery-powered, portable systems.

-Steve Harper

From the HP Journal Vol.34, N1, January 1983: article by Steve Harper.

### How fast is HP-IL - specifications and benchmarks

Transfer rate (bytes/sec): 8K (copying to a loop, no devices on loop); 6.4K (copying in a file); 4.5K (OUTPUT statement, no formatting (USING)); 4K (ENTER statement, no formatting (USING) and version 1B of the HP-IL module).

From the HP-71B specifications in the HP Catalog, 1987, p.61

- Using the HP-71B (best HP-IL controller) a realistic figure is 4 to 6 kB/s max.

- Using the HP Portable Plus, the performance is limited to the speed of the external devices to about 2-3 kB/s

| DISC E              | BENCHMARKS      |            |

|---------------------|-----------------|------------|

| Disc                | Speed           | Interleave |

| 9114 DS 3.5"        | 3.5Kb/S         | 4          |

| 9121 SS 3.5"        | 1.7Kb/S *       | ?          |

| 9122 DS 3.5"        | 1.7Kb/S *       | ?          |

| 8290× 5.25"         | 1.7Kb/S *       | ?          |

| 913x hard disc      | 1.7Kb/S *       | NA         |

|                     |                 |            |

| * 82169A HP-IL/HPIB | Converter speed | limit      |

| PPAGE100            |                 | PACKARD    |

From a HP Portable Plus (HP110 Plus) training. http://www.jeffcalc.hp41.eu/hpplus/files/slides mass storage.pdf

### How fast is HP-IL - measurements

Benchmark on HP-71B, using the sequence:

1 RESTORE IO @ SEND UNL MTA

2 T=TIME @ COPY HPILROM TO :LOOP @ T=TIME-T

3 DISP 16384/T;" bytes/s"

### Results:

| HP-71B + HP-IL loopback test                         | 8.5 kB/s                             |

|------------------------------------------------------|--------------------------------------|

| HP-71B + 1 device (HP9114A)                          | 8.7 kB/s (yes, faster!)              |

| HP-71B + 3 devices (HP9114A, HP82163B, HP82164A)     | 8.7 kB/s                             |

| ■ HP-71B + 5 devices ( + HP3468A, HP5384A)           | 7.4 kB/s                             |

| ■ HP-71B + HPIL/HPIB (HP82169A) mailbox mode         | 4.3 kB/s                             |

| ■ HP-71B + HPIL/HPIB (HP82169A) translator mode      | 2.6 kB/s                             |

| ■ HP-71B + PIL-IO board (v2.0)                       | 3.5 kB/s (no USB)                    |

| ■ HP-71B + PIL-Box (v2.1, ILPer stopped/bypass mode) | 3.5 kB/s (no USB traffic, as PIL-IO) |

|                                                      | ,                                    |

| HP-71B + PIL-Box (v2.1, 230 kbps, ILPer running)     | 1.8 kB/s (optimized config.)         |

### How fast is HP-IL – PIL-Box optimization

- The bottleneck for the PIL-Box performance is the USB link.

- USB is not efficient for the byte-per-byte communication of the HPIL.

- To get the best result, some optimization is needed.

- Use the benchmark sequence on HP-71B, to test the best configuration:

- 1 RESTORE IO @ SEND UNL MTA

- 2 T=TIME @ COPY HPILROM TO :LOOP @ T=TIME-T

- 3 DISP 16384/T;" bytes/s"

- Use the latest PIL-Box firmware (currently v2.1), try to use the 230 kbps com speed (jumper JP2 removed).

- Try the different USB ports.

- USB 3.0 ports may give better results.

- Try to use an external USB hub.

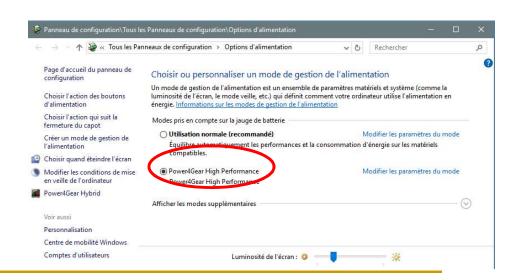

- Make sure the PC power option is using a 'High Performance' mode.

- Even with the best settings, performance is depending on each particular PC.

PIL-Box com setting (v2.1): JP2 installed: 115 kbps JP2 removed: 230 kbps

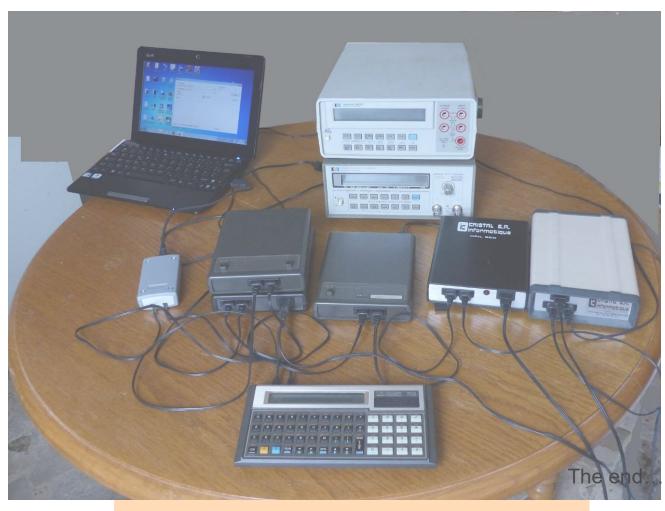

Thanks for your attention!