## SECTION 3

### CPU STRUCTURE AND OPERATION

This section explains the structure, addressing modes and operation of the central processing unit (CPU) in the HP-83/85.

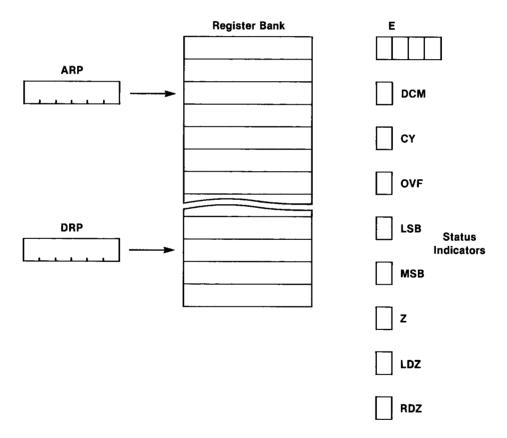

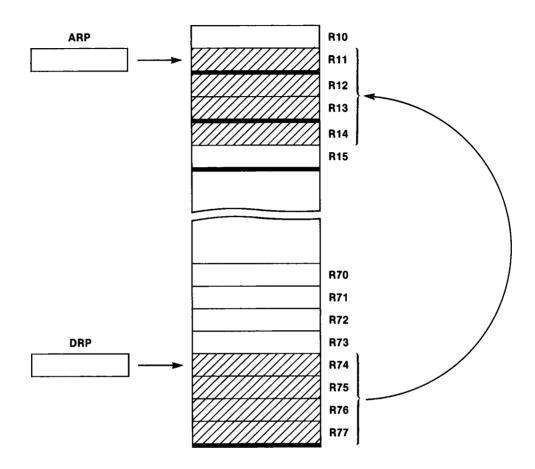

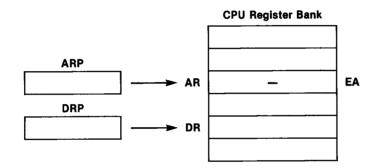

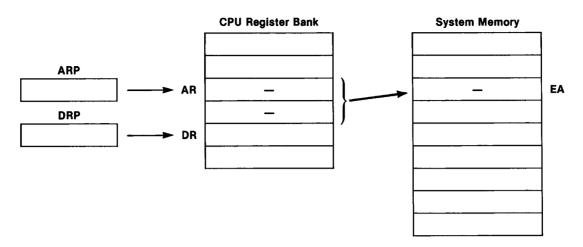

The HP-83/85 CPU consists of a  $64_{10}$ -byte register bank, a pair of address pointers called the address register pointer (ARP) and the data register pointer (DRP), an arithmetic and logic unit (ALU) and a shifter, and a set of status indicators.

**CENTRAL PROCESSING UNIT**

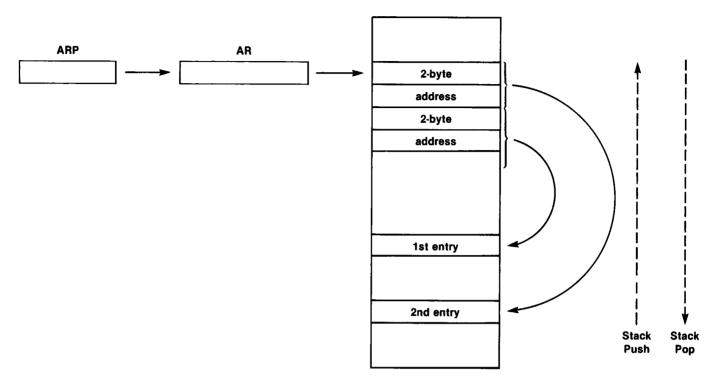

### ARP AND DRP

The address register pointer (ARP) and the data register pointer (DRP) are independent six-bit CPU locations. Both the ARP and the DRP can be used to address any of the bytes in the CPU register bank.

The CPU register addressed by the ARP is called the address register, or AR. The register addressed by the DRP is called the data register, or DR.

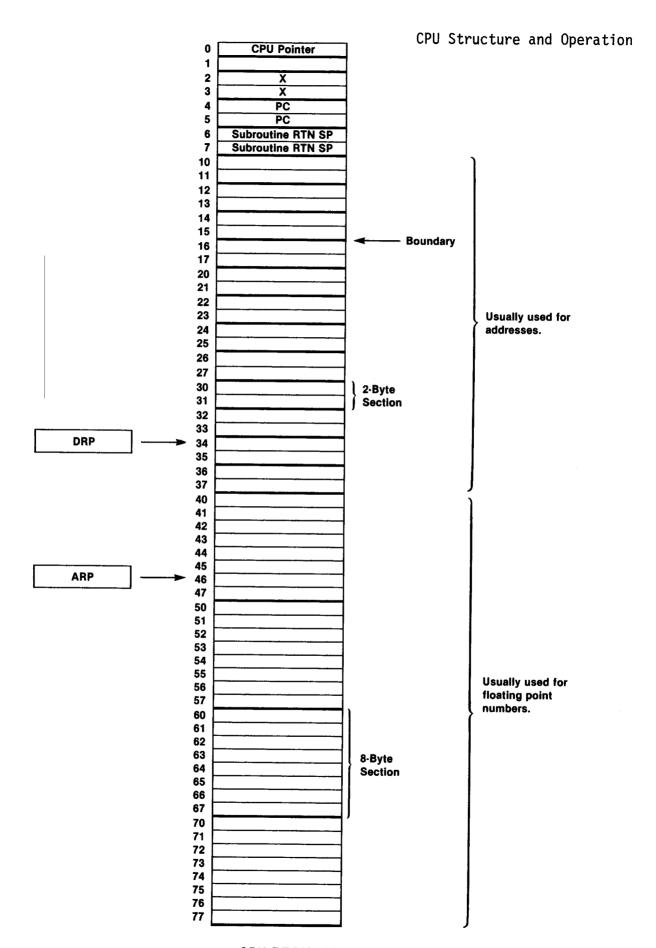

### CPU REGISTER BANK

The heart of the CPU is the register bank of 64 8-bit bytes of random-access memory. These bytes form registers which are grouped into two-byte (16-bit) sections and eight-byte (64-bit) sections. The diagram on the following page shows the organization of the CPU registers, which are numbered from 0 to  $77_8$ , and specified by RØ - R77.

Some of the registers in the CPU register bank are dedicated by hardware to specific tasks.

### HARDWARE-DEDICATED REGISTERS

The first  $40_8$  registers of the CPU (RØ - R37) are divided into two-byte (16-bit) sections. Of these, many of the bytes are reserved by hardware for use as special-purpose registers. These hardware-dedicated registers are:

<u>Register Bank Pointer</u>. Register 0 is a pointer to the remainder of the CPU register bank. Register 1 is inaccessible except through register 0.

<u>Index Scratch</u>. Registers 2 and 3 are scratch registers used for indexed addressing (X). Their contents are destroyed by execution of instructions using indexed addressing.

Program Counter. Registers 4 and 5 contain the program counter (PC).

**CPU REGISTER BANK**

<u>Return Stack Pointer</u>. Registers 6 and 7 contain the pointer for the subroutine return stack. (The space allocated for this stack in the computer's system memory comprises addresses 101300 through 101777, although sometimes these addresses may be used for other purposes.)

In addition to the special-purpose registers described above, certain other CPU registers are commonly used for specific purposes by internal HP-83/85 routines. (For example, registers R40 and R50 are used by internal mathematics routines for addition, subtraction, etc.)

### REGISTER BOUNDARIES

The CPU registers are separated by <u>boundaries</u>, shown as heavy lines in the illustration of the register bank above. In the first 32 bytes, there is a boundary every two bytes. In the next 32 bytes, there is a boundary every eight bytes.

This partitions the first 32 bytes into 16-bit sections (used primarily for address manipulation) and the next 32 bytes into 64-bit sections (used primarily for floating point quantities). The register array is, therefore, capable of holding up to four floating-point numbers and twelve 16-bit addresses.

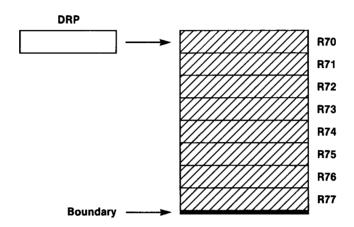

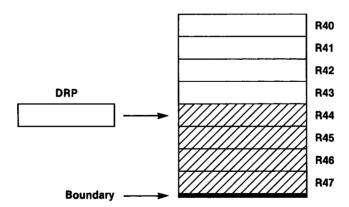

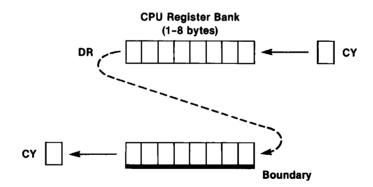

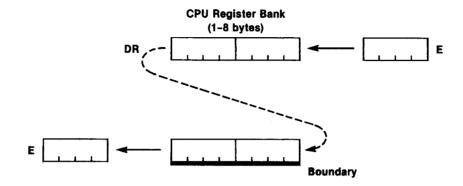

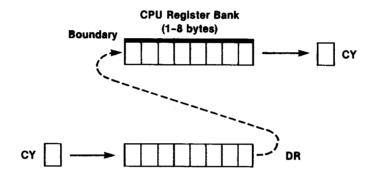

### MULTI-BYTE OPERATIONS

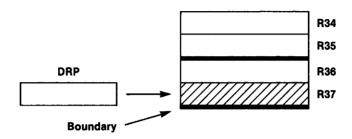

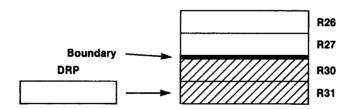

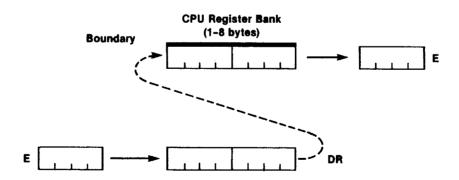

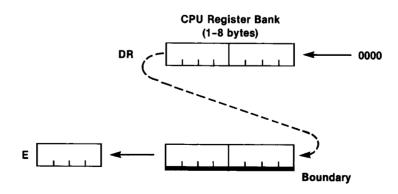

The HP-83/85 CPU structure permits "multi-byte operations," involving a string of bytes rather than just a single byte. A string can consist of from one to eight consecutive CPU registers. The exact number is determined by the DRP and the next boundary.

The locations involved in a multi-byte operation are those beginning with the location pointed to by the DRP and ending with the next boundary. The next boundary is the one in the direction of <u>increasing</u> addresses (except in the case of a shift right instruction.)

The following examples should help explain this concept:

--A multi-byte increment with DRP set to 70 (that is, executing ICM R70) results in an increment of the 64-bit quantity stored between locations R70 and R77. Higher addresses always refer to more significant bytes.

--A multi-byte test with DRP set to 44 (that is, executing TSM R44) results in the status flags being set according to the data found in registers R44, R45, R46 and R47. Location R47 is the most significant byte.

CPU Structure and Operation

--A multi-byte complement with DRP set to 37 (that is, executing TCM R37) complements only R37.

The only exception to the rule that the next boundary is in the direction of increasing addresses is the shift right instruction. If a multi-byte instruction is a shift right, then the next boundary is the one in the direction of decreasing addresses.

### Thus:

--A multi-byte shift right with DRP set to 31 (that is, executing LRM R31) shifts the combined contents of R31 and R30 right. R31 is the most significant byte.

### SINGLE-BYTE OPERATIONS

Besides executing multi-byte instructions, the HP-83/85 CPU also executes instructions using single bytes. In a single-byte operation, the DRP refers to only a single byte.

### TWO-OPERAND OPERATIONS

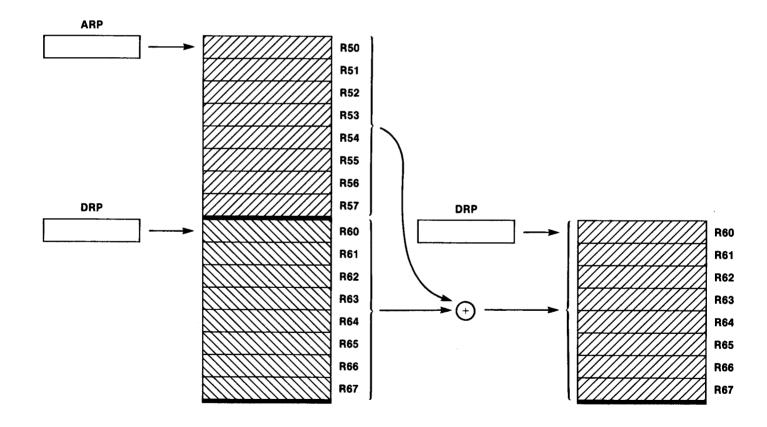

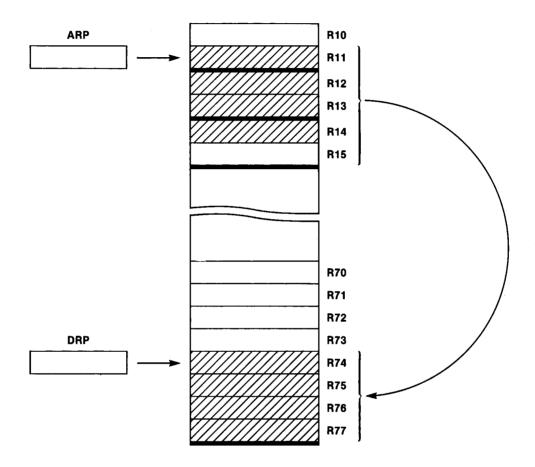

Two-operand multi- and single-byte instructions may also be executed. In the case of a multi-byte two-operand instruction, DRP points to the first operand and ARP points to the second. DRP is still used to determine the number of bytes involved for the first operand. The other operand consists of the same number of bytes, beginning with the location to which the ARP points. For example:

--A multi-byte add with DRP set to 60 and ARP set to 50 (that is, executing ADM R60, R50) results in the 64-bit quantity starting with R50 being added to the 64-bit quantity starting with R60. The sum is stored in R60 through R67.

--A multi-byte load with DRP set to 74 and ARP set to 11 (that is, executing LDM R74, R11) transfers the contents of four bytes beginning with R11 to locations R74, R75, R76 and R77.

--A multi-byte store with DRP set to 74 and ARP set to 11 transfers the contents of R74 through R77 to the four consecutive locations beginning with R11.

Remember: The number of bytes in a multi-byte operation is always determined by the setting of DRP (not ARP) and the next boundary.

There are also two-operand operations where the DRP points to one operand and the second is located in the computer's memory. Once again, the number of bytes to be operated upon is determined by the DRP. The corresponding number of bytes are accessed from memory beginning with the calculated effective address.

### NUMBER REPRESENTATION

Numbers in the HP-83/85 are manipulated in a variety of formats. The user has the option of specifying quantities as octal, BCD or decimal. In addition, the internal quantities used in the HP-83/85 occur in various formats, depending on their use.

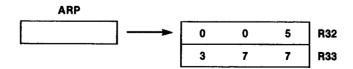

### **ADDRESSES**

An address, whether in the CPU register bank or in system memory, is always an octal value that occupies two bytes, or 16 bits. The lower-numbered byte contains the less significant byte of the address, and the higher-numbered byte contains the more significant byte of the address. Only the first byte of the two-byte address is referenced by other instructions.

For example, address 177405, translated into a binary quantity, appears like this:

When this binary quantity is split into two eight-bit registers, it appears as:

| <br>11 | 111 | 111 | 00 | 000 | 101 | Binary Quantity   |

|--------|-----|-----|----|-----|-----|-------------------|

| 3      | 7   | 7   | 0  | 0   | 5   | Register Contents |

Only the first byte of the two-byte address is referenced by other instructions, so an address pointing to ROM location 177405 from the CPU might look like this:

### NUMERIC QUANTITIES

Numeric quantities in the HP-83/85 may be of three types: Real, short, and integer. The following illustration shows how numeric quantities are represented internally in the computer. For the illustration, the numbers are shown in CPU registers R40 - R47.

| Real |     |     | Integer |    |    | Short |           |    |

|------|-----|-----|---------|----|----|-------|-----------|----|

| 40   | E1  | E2  | 45      | D1 | D0 | 44    | E0        | E1 |

| 41   | E0  | MS  | 46      | D3 | D2 | 45    | M3        | M4 |

| 42   | M10 | M11 | 47      | s  | D4 | 46    | M1        | M2 |

| 43   | M8  | M9  | _       |    | •  | 47    | 0 0 SM SE | MO |

| 44   | M6  | M7  |         |    |    |       |           |    |

| 45   | M4  | M5  |         |    |    |       |           |    |

| 46   | M2  | МЗ  |         |    |    |       |           |    |

| 47   | MO  | M1  |         |    |    |       |           |    |

### FORMATS OF NUMERIC QUANTITIES

In real or floating-point format, the mantissa is a 12-digit quantity expressed as a magnitude. Each digit consists of four bits. The least significant digit, represented by M11, is stored in R42. The most significant digit, represented by MØ, is stored in R47. The number is normalized; thus, there is an implied decimal point between MØ and M1 in R47. The sign of the mantissa is stored in the least significant digit of R41. A zero is stored as the sign of the mantissa if the number is positive; otherwise, a nine is stored. The exponent is a three-digit number stored in R40 and in the most significant digit position of R41. Exponents are expressed in ten's complement form.

Integer variables are stored in three bytes, with five digits and a sign. Short variables are stored as a mantissa sign (SM) an exponent sign (SE), five mantissa digits, and a two-digit exponent.

### STATUS INDICATORS

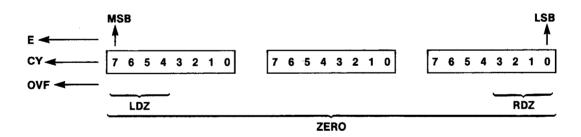

The HP-83/85 CPU contains eight flags and a four-bit register for program status. The flags signal the present condition of the data, while the four-bit register serves as an "extended" register for counting and data manipulation.

Status can affect or be affected by CPU instructions. In the HP-83/85 CPU, the instruction set has data movement instructions of both the arithmetic and non-arithmetic types. These instructions include:

--Arithmetic: Add, subtract, compare, increment, decrement, complement.

--Non-arithmetic: Load, store, logical and, or, exclusive or, shift, clear, test.

The following status indicators are present in the HP-85 CPU:

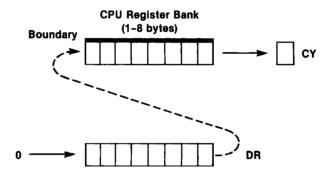

E: <u>Extend Register</u>. A four-bit register which can be cleared, incremented, or decremented independent of DCM. Shifts can be made into and out of the extend register only when DCM is set.

DCM: <u>Decimal Mode Flag</u>. When set, binary-coded decimal (BCD) operations will be performed. When cleared, binary operations will be performed. The operations affected by DCM are all the arithmetic data movement instructions and the shift instructions. The DCM flag can be modified only by two CPU instructions, BCD and BIN. The BCD instruction sets DCM, while the BIN instruction clears DCM.

CY: <u>Carry Flag</u>. This one-bit register can be shifted into and out of when DCM is cleared (i.e., BIN mode). It is loaded with the carry from the most significant bit (MSB) according to the table shown here:

| CPU Instruction | Carry Flag                                                                                             |

|-----------------|--------------------------------------------------------------------------------------------------------|

| Add             | CY set according to carry of add.                                                                      |

| Subtract        | CY set if result is positive, cleared if result is negative.                                           |

| Compare         | Same setting as for subtract.                                                                          |

| Increment       | CY set as for add.                                                                                     |

| Decrement       | CY set as for subtract.                                                                                |

| Shift           | CY loaded with bit shifted out, if in binary mode. (Right shift loads CY from LSB.)                    |

| Complement      | CY cleared by nine's complement, set by ten's complement, if contents of data register (DR) were zero. |

All other data movement instructions clear CY.

OVF: Overflow Flag. The overflow flag is set whenever the result of a binary arithmetic operation exceeds the maximum positive or negative number that can be contained in the destination register. This can occur as the result of a compare, binary add, binary subtract, binary complement, or binary left shift instruction. Thus, an arithmetic data movement instruction or a left shift with DCM cleared affects OVF; all other data movement instructions clear OVF. The remaining instructions do not affect OVF.

LSB: <u>Least Significant Bit Flag</u>. LSB is set the same as the least significant bit (LSB) of the result of each data movement instruction.

CPU Structure and Operation

MSB: Most Significant Bit Flag. MSB is set the same as the most significant bit (MSB) of the result of each data movement instruction.

Z: Zero Flag. Z is set if a data movement instruction produces a result of all zeros. If the result is not all zeros, Z is cleared. Other instructions do not affect Z.

LDZ: <u>Left Digit Zero Flag</u>. LDZ is affected only by data movement instructions. LDZ is set if the most significant nibble (four bits) of the result is 0000. If the most significant four bits are not 0000, LDZ is cleared.

RDZ: Right Digit Zero Flag. RDZ is affected only by data movement instructions. RDZ is set if the least significant nibble (four bits) of the result is 0000, regardless of the setting of DCM. If the most significant four bits are not 0000, RDZ is cleared.

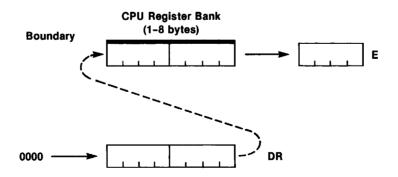

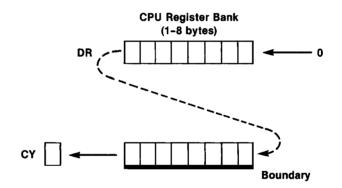

Status information is based on the entire single or multi-byte quantity that is processed. The figure below illustrates status on a three-byte quantity.

**MULTI-BYTE STATUS**

All multi-byte operations except right shift start execution with the least significant byte. All status flags except LSB, RDZ, and DCM are updated after each byte of an operation, and therefore will be correct whenever the memory boundary is reached. The LSB and RDZ flags are set only for the first byte.

For a shift right instruction, where the shift is from the most significant byte to the least significant, the MSB and LDZ flags are set only for the most significant byte; the rest are updated after each byte.

For a complete list of all CPU instructions and their relationships to status indicators, refer to section 4 and appendix C.

### SECTION 4

### ASSEMBLER INSTRUCTIONS

The HP-83/85 Assembler instructions can manipulate data in the HP-83 or HP-85 central processing unit, and through the CPU, in HP-83/85 RAM as well.

Assembler instructions are of two types: Instructions and pseudo-instructions. Instructions operate directly on the CPU and during assembly are translated directly into machine language object instructions. They are specified by means of opcodes. Pseudo-instructions are entered in the same way as CPU instructions, but they are actually messages to the Assembler ROM. They are specified by means of pseudo-opcodes.

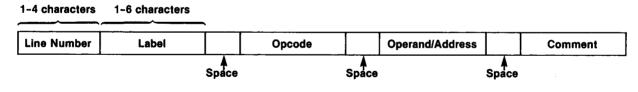

### ENTERING INSTRUCTIONS AND PSEUDO-INSTRUCTIONS

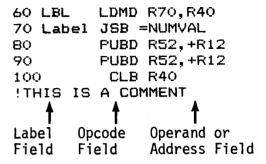

Source code is typed into the CRT by entering the line number, followed by a label (if any), followed by the opcode, followed by the address or operand, if required, followed by a comment (if any). When [END LINE] is then pressed, the line is parsed and the elements are assigned to their respective fields on the CRT.

SOURCE CODE INSTRUCTION FORMAT

In assembler mode, the HP-83/85 is sensitive to spacing among the elements of a line of source code. For example:

A statement entered to the CRT as:

60 LBL LDMD R70,R40

70 Label jsb=numval

80 PUBD R52,+R12

90 PUBD 52,+12

100 CLB R40 !THIS IS A COMMENT

After parsing appears as:

### LINE NUMBERING

Each line of binary program source code must begin with a line number. These line numbers may be entered individually, or automatic line numbering may be specified with the [AUTO] key.

These line numbers are useful for entering and editing a binary program, but do not correspond to the addresses of the machine language object code that is generated during assembly.

### **LABELS**

No spaces or one space may be typed between the line number and the label field. A label is optional, and may be from one to six characters. A label cannot have a digit as the first character, nor a space as any character; one or more spaces denote the end of the label.

When a label has been entered and parsed, it appears in a label field on the CRT or printer. This field begins in the second character space to the right of the line number.

### OPCODES AND PSEUDO-OPCODES

The opcodes and pseudo-opcodes for assembly language instructions may be entered after typing at least two spaces after the line number or at least a single space after a label. Entries in the opcode field are restricted to valid instructions and pseudo-instructions. Blanks are not allowed within the opcode field.

When an opcode or pseudo-opcode has been entered and parsed, it begins in the field nine spaces to the right of the line number.

Opcodes (but not pseudo-opcodes) may be either single-byte (specified by a "B") or multi-byte (specified by an "M").

### OPERANDS OR ADDRESSES

Depending upon the format of the instruction, the operand or address field may specify one or more of the following:

- -- Data Register. A CPU register which may signify single-byte or multi-byte operation.

- -- Operand. May be a CPU register or a memory location. Depending on the addressing mode, memory can be addressed immediately, indirectly, or by an index.

- --Register Pointer. Constant used to load ARP or DRP.

- --Label. A label to specify an address or constant.

- --Nothing. Some instructions do not require an entry in this field.

An AR or DR in the CPU is specified by an "R" before the register number (e.g., R32), or by an "X" before the register number when indexed addressing is used. The "R" may be omitted when CPU register numbers are typed, since the assembler inserts a missing "R" automatically. The "X" must be typed to indicate register numbers for indexed operations.

### COMMENTS

A comment or remark must begin with an exclamation point. A comment must be typed beginning in the first or second space after the line number, or beginning one or more spaces after the other elements of the line of source code.

After being parsed, a comment which has been entered immediately following the other elements of the line begins in column 33; thus, on the HP-83/85 CRT it appears on the following line. A peripheral printer with a column width greater than 32 can permit a comment to appear on the same line as the source code statement.

### NUMERIC VALUES

Numeric values can be entered in octal, BCD or decimal notation. A BCD value is entered by immediately following the value with a "C," while a decimal value is followed by a "D;" otherwise the assembler assumes octal values.

Example: LDM R45,=31, 19C, 25D Loads the same bit pattern into registers R45, R46 and R47.

Registers can be specified by octal values only.

### SYNTAX AND SYMBOLS USED

The following shows the syntax guidelines once again and also includes a list of the symbols used in the descriptions of assembler instructions.

- LDB Instructions shown in capital letters, but not underlined, must be entered exactly as shown (in either upper-case or lower-case letters).

- Items shown underlined (e.g.,  $\underline{DR}$ ) are expressions or names that must be specified in the instruction, statement, or command.

- [ ] Items shown between brackets are optional. (e.g., CMB[D] indicates there is a CMB instruction and also a CMBD instruction available.) If several items are stacked between brackets, any one or none of the items may be specified.

- ... Three dots (ellipsis) following a set of brackets indicate that the items between the brackets may be repeated.

- Is transferred to.

- ( ) Contents of.

- Complement (e.g.,  $\overline{x}$  is complement of x). This is one's complement if DCM=0 and nine's complement if DCM=1.

- B/M Single-byte or multi-byte instruction.

- AR Address register location—location of first byte addressed by ARP. Can be a register (e.g., R32), R\* or R#.

- DR Data register location--location of first byte addressed by DRP. Can be a register (e.g., R32), R\* or R#.

- Address mode for load/store. Can be blank (for immediate), D (for direct), or I (for indirect).

- ARP Address Register Pointer. A 6-bit register used to point to one of 64 CPU registers. The byte to which ARP points is often used as the first of two consecutive bytes forming a memory <u>address</u>.

- DRP Data Register Pointer. A 6-bit register used to point to one of 64 CPU registers. The location to which DRP points is often used as the destination for data loaded into the CPU.

- R(x) CPU register addressed by (x).

- M(x) Memory location addressed by (x). (x) must be a 16-bit address.

- PC Program Counter. CPU registers R4 and R5. Used to address the instruction being executed.

- SP Subroutine Stack Pointer. CPU registers 6 and 7. Used to point to the next available location on the subroutine return address stack.

- EA Effective Address. The location from which data is read for load-type instructions or the location where data is placed for store-type instructions.

- ADR Address. The two-byte quantity directly following an instruction that uses the literal direct, literal indirect, index direct or index indirect addressing mode. This quantity is always an address.

The following pages show the HP-83/85 Assembler ROM instructions that are used to manipulate the CPU and external memory. These instructions are illustrated in an abbreviated form in this section; for a complete list of all forms of each instruction, refer to appendix C.

Also contained in this section are the Assembler ROM pseudo-instructions.

### LOAD/STORE INSTRUCTIONS

The instructions for loading and storing data have access to all eight addressing modes, and they can be single-byte or multi-byte.

LD

CPU Instruction

Load

Format:

LDBA DR, operand

Single byte

LDMA DR, operand

Multi-byte

Operation:

DR←(EA)

Description: Data register is loaded with the contents of the effective address

determined by the operand and the addressing mode.

ST

CPU Instruction

Store

Format:

STBA DR, operand

Single byte

STMA DR, operand

Multi-byte

Operation:

(DR)→EA

Description: Contents of data register are stored in effective address deter-

mined by the operand and the addressing mode.

### ADDRESSING MODES

The HP-83/85 CPU allows for several addressing modes. These include literal, register, indexed and stack modes of memory access.

Not all addressing modes are available to all instructions. The load (LD) and store (ST) instructions have access to all addressing modes except stack addressing, and they are used here for illustration: For a list of the addressing modes available to any particular instruction, consult the description of that instruction in this section or in appendix C.

In addressing, all addresses are referred to as two-byte quantities. Because all addresses are two consecutive bytes, only the first byte of the sequence is referenced. For instance, the AR is actually a single byte within the CPU register bank that is pointed to by the ARP. When the AR is described as being an address, remember that R (ARP) contains the low byte of the address and R (ARP + 1) contains the upper byte of the address.

The multi-byte feature of the CPU allows data to be manipulated in quantities of from one to eight bytes. Therefore, in the following descriptions, only the address of the first byte of data is specified. As explained earlier, the number of bytes is determined by the distance of the DR from the next consecutive boundary.

In the following descriptions, the effective address (EA) points to the first byte of data to be loaded for load instructions.

For store instructions, EA points to the location where the first byte of data is stored.

### REGISTER MODE

The first category of addressing is the <u>register</u> addressing mode. This mode allows the CPU registers  $(64_{10})$  bytes) to be used as addresses as well as for data. There are three levels of register addressing modes.

REGISTER IMMEDIATE

Format:

Opcode B/M DR, AR

Effective

Address:

AR

Description: The operand is another CPU register (single or multi-byte) beginning at AR. Thus, the AR is the source for load instructions or the destination for store instructions.

### REGISTER IMMEDIATE ADDRESSING

Examples:

LDB R36, R32 Loads contents of R32 into CPU register R36.

STM R40, R50 Stores contents of registers R40 through R47 into

registers R50 through R57.

REGISTER DIRECT

Format:

Opcode B/M D DR, AR

Effective

Address:

M(AR)

Description: The effective address is a location in system memory that is addressed by the AR. This mode is useful when using a CPU register as a pointer to system memory.

### REGISTER DIRECT ADDRESSING

Examples:

LDBD R36, R32 Loads CPU register R36 with the contents of the system memory location addressed by R32-R33.

STMD R40, R50 Stores contents of R40-R47 into system memory beginning with location addressed by R50-R51.

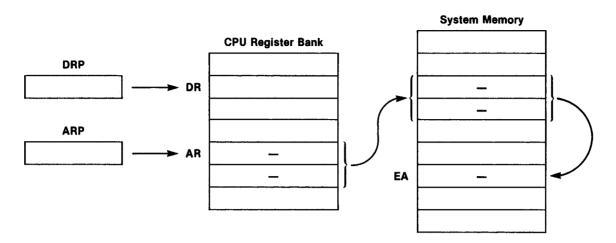

### REGISTER INDIRECT

Format:

Opcode B/M I DR, AR

Effective

Address:

M(M(AR))

Description: The address register points to a system memory location, which in turn points to another memory location that is the effective address.

### REGISTER INDIRECT ADDRESSING

Example:

LDBI R36, R32 If R32 and R33 contain the address 105371, loads CPU register R36 with the contents of the memory location that is addressed by the contents of system memory locations 105371 and 105372.

### LITERAL MODE

The second of the categories of address modes is the literal mode. In literal mode, the operand is a literal quantity stored in memory immediately following the opcode. A literal string can be:

- --BCD constant, e.g., 99C, ..., 79C ( $\leq$  10<sub>8</sub> bytes)

- --Octal constant, e.g., 12, ..., 277 ( $\leq 10_8$  bytes)

- --Decimal constant, e.g., 201D, ..., 9D ( $\leq$  10<sub>8</sub> bytes)

- --Label (The literal quantity is a one- or two-byte value or address assigned to the label.)

The programmer is responsible for ensuring that the number of bytes of the literal string matches the DRP setting. The assembler does <u>not</u> check for mismatch.

There are three types of literal addressing modes.

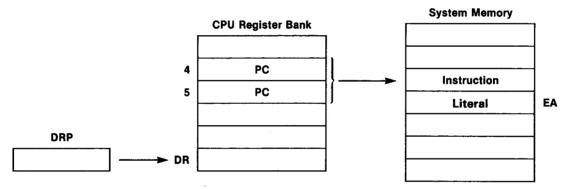

### LITERAL IMMEDIATE

Format:

Opcode B/M DR, = literal

Effective

Address:

(PC+1)

Description:

The operand is a literal string that, during assembly, is stored in memory immediately after the instruction opcode. This mode is useful for loading constants into the CPU register bank.

LITERAL IMMEDIATE ADDRESSING

Examples:

LDB R36, = 3D Loads  $3_{10}$  into CPU register R36.

LDM R40, = 0,0,0,0,0,0,0,120 Loads  $120_8$  (i.e., a floating-point 5) into registers R40-R47.

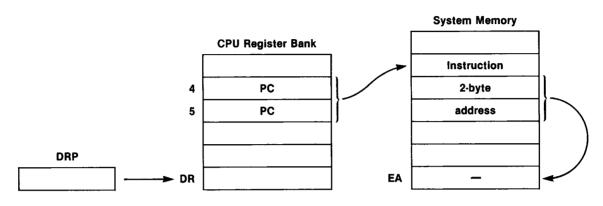

LITERAL DIRECT

Format:

Opcode B/M D DR, = label

**Effective**

Address:

M(PC+1)

Description: The operand is a memory location that, after assembly, is addressed by a two-byte literal quantity stored immediately after the instruction opcode. The label defines the two-byte literal quantity to be used by the Assembler ROM.

LITERAL DIRECT ADDRESSING

Examples:

LDBD R34, = ROMFL Loads the contents of the memory location addressed by the label ROMFL into CPU register R34.

Stores contents of CPU registers R74 through STMD R74, = CHIDLE R77 into four memory locations beginning with the location addressed by the label CHIDLE.

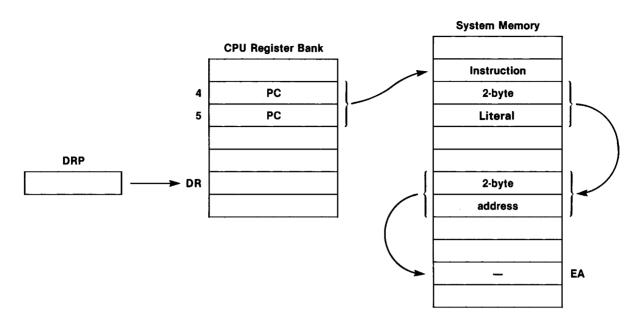

### LITERAL INDIRECT

Format:

Opcode B/M I DR, = label

Effective

Address:

M(M(PC+1))

Description: The operand is a memory location that, after assembly, is addressed by a two-byte memory location that itself is addressed by a two-byte literal quantity stored immediately after the instruction opcode. The label defines the two-byte literal quantity used by the Assembler ROM.

### LITERAL INDIRECT ADDRESSING

Example:

STBI R30, = ADDR Stores the contents of CPU register R30 into the memory location addressed by another memory location which is itself addressed by the two-byte literal quantity specified by the label ADDR.

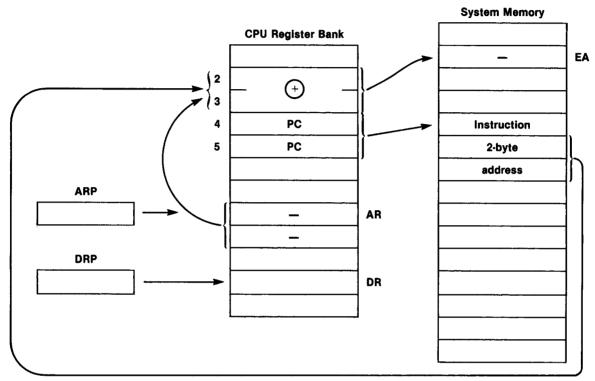

### INDEX MODE

The index mode is the third addressing category. Indexing is useful for accessing data when the data is stored in a table. In indexed addressing, a fixed base address is added to an offset to create the desired address. The CPU performs this addition using CPU registers 2 and 3. After an index instruction, registers 2 and 3 contain the effective address (i.e., the sum of the base and the offset). Neither the original base nor the offset is altered in memory. There are two modes for indexed addressing.

### INDEX DIRECT

Format:

Opcode B/M D DR, XAR, label

Effective

Address:

M(AR+(PC+1))

Description: The effective address is found by adding (in binary) the two-byte contents of the AR to the two-byte address that immediately follows the instruction opcode in memory.

INDEXED DIRECT ADDRESSING

Example:

LDBD R36, X30, TABLE Loads into CPU register R36 the contents of the memory location addressed by registers R2 and R3. R2 and R3 contain the sum of the contents of R30 and the contents of the address TABLE.

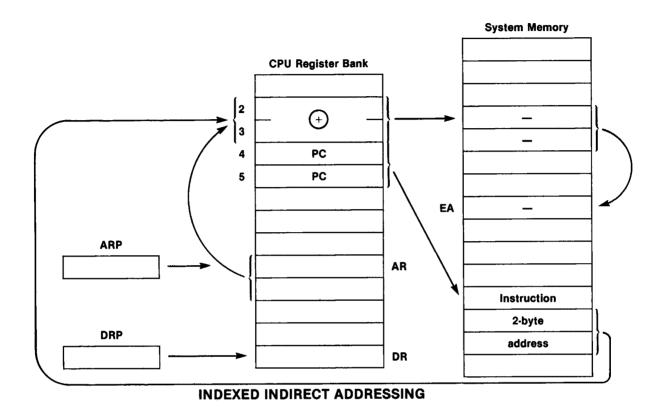

### INDEX INDIRECT

Format: Opcode B/M I

Opcode B/M I DR, XAR, label

Effective

Address: M(M(AR+(PC+1)))

Description: The effective address is found in a memory location. This memory

location is found by adding (in binary) the two-byte contents of

the AR to the two-byte address that immediately follows the instruction opcode in memory. This mode is useful when addresses are stored in table form.

Example:

STMI R36, X30, OFFST Stores the contents of CPU register R36 and R37 in memory, beginning with the location addressed by another memory location which is itself addressed by CPU registers 2 and 3. Registers 2 and 3 contain th sum of the address in R30 plus the offset specified by the label OFFST.

### STACK INSTRUCTIONS

There is a large set of instructions that are available to push data onto and pop data from stacks in the main memory of the HP-83/85. These stacks can be addressed by the instructions using direct or indirect addressing.

P[] CPU Instruction

Push

Format: PUB D/I DR +/- AR Push single byte

PUM <u>D/I DR +/- AR</u> Push multi-byte

Description: Pushes single byte or multi-byte onto stack. D/I indicates direct

or indirect addressing. +/- indicates stack pointer is incremented

(increasing stack) or decremented (decreasing stack) in memory.

Examples: PUBD R32, +R12

PUBI R32, -R46

PO CPU Instruction

Pop

Format: POBD/I DR +/-AR Pop single byte

POMD/I DR +/- AR Pop multi-byte

Description: Pops single byte or multi-byte off stack. D/I indicates direct or

indirect addressing. +/- indicates stack pointer is incremented (increasing stack) or decremented (decreasing stack) in memory.

### STACK ADDRESSING

CPU registers R6 and R7 are permanently dedicated, and always contain the address of the subroutine return stack. CPU registers R12 and R13 contain, by convention, the address of the operational stack used during runtime by many of the internal HP-85 routines. The user can, of course, address a stack from nearly any CPU register pair.

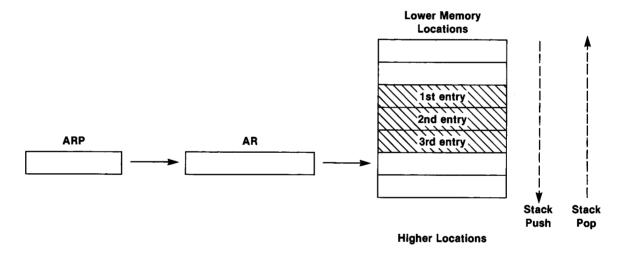

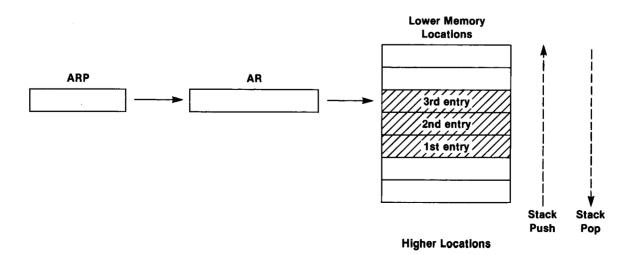

Stacks may be <u>increasing</u> or <u>decreasing</u>. An increasing stack is one which is filled in the direction of higher memory locations and from which data is removed in the direction of lower memory locations. In a decreasing stack, data is

pushed in the direction of lower memory locations, and taken off in the direction of higher memory locations. To avoid confusion, it is best to address a particular stack using only instructions for an increasing stack or only instructions for a decreasing stack, but not both.

For stack addressing, the stack pointer is contained in the AR. Multiple stacks are handled by having multiple stack pointers within the CPU register space. A stack is activated by setting ARP equal to the location of that stack's pointer.

For an increasing stack, the AR must point to the next available location on the stack. For a decreasing stack, the AR points to the occupied location on top of that stack.

### **INCREASING STACK**

**DECREASING STACK**

### STACK DIRECT

In this addressing mode, the stack is presumed to contain data. Stores to the stack (pushes) fill the stack. Loads from the stack (pops) empty the stack.

For a push onto an increasing stack, the AR points to the location where data is to be stored. Following the store, the AR is incremented by the number of bytes stored. For a pop operation from an increasing stack, the AR is first decremented by the number of bytes to be popped off. The AR then points to the location of the data to be removed from the stack.

For a pop from a decreasing stack, the AR points to the location of the data to be removed. Following the removal, the AR is incremented by the number of bytes moved. For a push operation onto a decreasing stack, the AR is first decremented by the number of bytes to be stored on the stack. Then the data is pushed onto the stack.

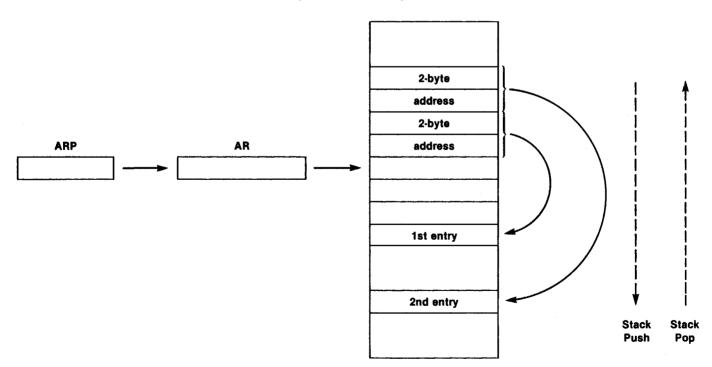

### STACK INDIRECT

In this addressing mode, the stack is presumed to contain an ordered list of addresses. These addresses point to the location from which data is read by pops or to the location into which data is stored by pushes.

For a push onto an increasing stack, the AR points to the effective address. After storing data in M(EA), the AR is incremented by two. For a pop instruction from an increasing stack, the AR is first decremented by two in order to point to the effective address. M(EA) is then loaded into the CPU register designated by the DRP.

### INSTRUCTIONS FOR AN INCREASING STACK

An increasing stack is one which is pushed in the direction of higher addresses (+) and popped in the direction of lower addresses (-).

## Lower Memory Locations 1st entry 2nd entry Stack Stack Push Pop Higher Locations

### I (Indirect Mode)

Each entry can be one or more bytes

### **INCREASING STACK**

The instructions available for use with an increasing stack are:

| PUBD DR, +AR                | Push byte direct with increment         |

|-----------------------------|-----------------------------------------|

| PUMD <u>DR</u> , +AR        | Push multi-byte direct with increment   |

| PUBI <u>DR</u> , +AR        | Push byte indirect with increment       |

| PUMI <u>DR</u> , +AR        | Push multi-byte indirect with increment |

| POBD DR, -AR                | Pop byte direct with decrement          |

| POMD <u>DR</u> , <u>-AR</u> | Pop multi-byte direct with decrement    |

| POBI <u>DR</u> , <u>-AR</u> | Pop byte indirect with decrement        |

| POMI <u>DR</u> , <u>-AR</u> | Pop multi-byte indirect with decrement  |

### INSTRUCTIONS FOR A DECREASING STACK

A decreasing stack is one which is pushed in the direction of lower addresses (-) and popped in the direction of higher addresses (+).

# ARP AR 3rd entry 2nd entry 1st entry Higher Locations Higher Locations

### I (Indirect Mode)

Each entry can be one or more bytes

### **DECREASING STACK**

The instructions available for use with a decreasing stack are:

| PUBD <u>DR</u> , <u>-AR</u> | Push byte direct with decrement         |

|-----------------------------|-----------------------------------------|

| PUMD DR, -AR                | Push multi-byte direct with decrement   |

| PUBI <u>DR</u> , <u>-AR</u> | Push byte indirect with decrement       |

| PUMI <u>DR</u> , <u>-AR</u> | Push multi-byte indirect with decrement |

| POBD <u>DR</u> , <u>+AR</u> | Pop byte direct with increment          |

| POMD DR, +AR                | Pop multi-byte direct with increment    |

| POBI <u>DR</u> , <u>+AR</u> | Pop byte indirect with increment        |

| POMI <u>DR</u> , <u>+AR</u> | Pop multi-byte indirect with increment  |

### ARITHMETIC AND LOGICAL INSTRUCTIONS

The arithmetic and logical instructions consist of add, subtract, compare, logical AND and logical OR instructions.

AD Add CPU Instruction

Format:

ADB [D] DR, operand

Add byte

ADM [D] DR, operand

Add multi-byte

Operation:

DR ← DR + operand

Description: Add single or multi-byte. The contents of the effective address determined by the addressing mode are added to the DR. If DCM=1, BCD addition is performed; otherwise, binary addition is performed.

The result is stored in the data register.

Examples:

ADB R40, R50

ADMD R30.=LABEL

ANM

CPU Instruction

Logical AND

Format:

ANM [D] DR, operand

Operation:

DR ← DR • operand

Description: The DR is loaded with the logical AND of itself and the contents

of the effective address determined by the addressing mode used.

This instruction is multi-byte only.

Examples:

ANM R40, R50

ANMD R32,=LABEL

CM

CPU Instruction

Compare

Format:

CMB [D] DR, operand

Compare byte

CMM [D] DR, operand

Compare multi-byte

Operation:

DR + ten's complement of operand if BCD mode set

DR + two's complement of operand if binary mode set

Description: Compares operand with data register(s). The contents of the effective address determined by the operand and the addressing mode are subtracted from DR. BCD subtraction is performed if DCM=1; otherwise a binary subtraction is performed. The result is used to affect CPU status indicators and is not stored; DR is not affected.

Examples:

CMB R24,=377

CMM R22, R32

OR

CPU Instruction

Logical OR (Inclusive)

Format:

ORB DR, AR

Inclusive OR (single byte)

ORM DR, AR

Inclusive OR (multi-byte)

Operation:

$DR \leftarrow DR \vee AR$

Description: Contents of DR are replaced with inclusive OR of DR and AR. CY and

OVF are cleared.

Examples:

ORB R21, R41

ORM R40, R70

SB

CPU Instruction

Subtract

Format:

SBB [D] DR, operand

Subtract byte

SBM [D] DR, operand

Subtract multi-byte

Operation:

DR + DR + ten's complement of operand if BCD mode

DR + DR + two's complement of operand if binary mode

Description: The contents of the effective address determined by the addressing mode and the operand are subtracted from the contents of the DR. BCD subtraction is performed if DCM=1; otherwise binary subtraction is performed. The result is stored in DR. CY is set if the result

is positive, cleared if the result is negative.

Example:

SBM R26,=177, 0

XR

CPU Instruction

Logical OR (Exclusive)

Format:

XRB DR, AR

Exclusive OR (single byte)

XRM DR, AR

Exclusive OR (multi-byte)

Operation:

DR + DR + AR

Description: Contents of DR are replaced with the exclusive OR of DR and AR.

CY and OVF are cleared.

Example:

XRM R40, R50

### SHIFT INSTRUCTIONS

All shift instructions can be BCD or binary. The shift instructions consist of logical left, logical right, extended left and extended right instructions; all are available in single byte or multi-byte modes.

EL Extended Left Shift CPU Instruction

Format:

ELB DR

Extended left shift byte

ELM DR

Extended left shift multi-byte

Description:

<u>Binary Mode</u>. In binary mode, the contents of DR (one to eight bytes) are shifted left one bit position. Carry flag CY is loaded from MSB. LSB is loaded from CY. OVF is set if the shift causes a sign change.

$\underline{\mathsf{BCD}}$  Mode. In BCD mode, the contents of DR (one to eight bytes) are shifted left one digit position (i.e., four bits) through the E register. CY is cleared.

ER

CPU Instruction

Extended Right Shift

Format:

ERB DR

Extended right shift byte

ERM DR

Extended right shift multi-byte

Description:

<u>Binary Mode</u>. In binary mode, the contents of DR (one to eight bytes) are shifted right one bit position. For multi-byte shifts, the shift proceeds from DR to the next lower boundary. Carry flag CY is loaded from LSB. MSB is loaded from CY.

<u>BCD Mode</u>. In BCD mode, the contents of DR (one to eight bytes) are shifted right one digit position (i.e., four bits) through the fourbit E register. CY is cleared.

Notice that a multi-byte right shift instruction, unlike other multi-byte instructions, proceeds from the DR to the preceding (i.e., lower-numbered) boundary.

Example:

ERM R47 Shifts all eight bytes of R40 - R47 right.

Logical Right Shift

LR

CPU Instruction

Format:

LRB DR

Logical right shift byte

LRM DR

Logical right shift multi-byte

Description:

<u>Binary Mode</u>. In binary mode, the contents of DR (one to eight bytes) are shifted right one bit position, and the MSB is cleared. For multi-byte shifts, the shift proceeds from DR to the next lower boundary. Carry flag CY is loaded from LSB.

<u>BCD Mode</u>. In BCD mode, the contents of DR (one to eight bytes) are shifted right one digit position (i.e., four bits), and the most significant digit is cleared. For multi-byte shifts, the shift proceeds from DR to the next lower boundary. The least significant digit is shifted into the four-bit E register.

Notice that a multi-byte right shift instruction, unlike other multi-byte instructions, proceeds from the DR to the preceding (i.e., lower-numbered) boundary.

Example: LRM R54 Shifts contents of R54, R53, R52, R51, and R50 right.

LL CPU Instruction

Logical Left Shift

Format: LLB DR Logical left shift byte

LLM <u>DR</u> Logical left shift multi-byte

Description: <u>Binary Mode</u>. In binary mode, the contents of DR are shifted left one bit position, and the LSB is cleared. The bit shifted out of MSB is saved in CY. OVF is set if the shift causes a sign change.

<u>BCD Mode.</u> In BCD mode, the contents of DR are shifted left one digit position (i.e., four bits), and the least significant digit is cleared. The digit shifted out of the most significant digit position is saved in the E register. CY is cleared.

Example:

LLM R45 Shifts contents of R45, R46, and R47 left one bit position through CY (in binary mode) or left one digit position through E (in BCD mode).

# REGISTER INCREMENT AND DECREMENT INSTRUCTIONS

The increment and decrement instructions for the CPU registers can be  $\ensuremath{\mathsf{BCD}}$  or binary.

DC.

CPU Instruction

Decrement

Format:

DCB DR

Decrement byte

DCM DR

Decrement multi-byte

Operation:

DR + DR + two's complement of 1 (binary mode)

DR + DR + ten's complement of 1 (BCD mode)

Description: Binary Mode. In binary mode, DR is decremented by 1 (binary).

OVF is set if this operation causes a sign to change to a positive

value. CY is set by decrementing a non-zero number.

BCD Mode. In BCD mode, DR is decremented by 1 (decimal). OVF is

cleared. CY is set by decrementing a non-zero number.

Example:

DCB R12

IC

CPU Instruction

Increment

Format:

ICB DR

Increment byte

ICM DR

Increment multi-byte

Operation:

$DR \leftarrow DR + 1$

Description: Binary Mode. In binary mode, DR is incremented in binary by 1.

OVF is set if this operation causes a sign change to a negative

value.

In BCD mode, DR is incremented in decimal by 1. OVF is

cleared.

Example:

ICM R40

# COMPLEMENT INSTRUCTIONS

The complement instructions can be BCD or binary.

NC

CPU Instruction

Nine's (Or One's) Complement

Format:

NCB DR

Nine's (or one's) complement byte

NCM DR

Nine's (or one's) complement multi-byte

Operation:

$DR \leftarrow \overline{DR}$

Description: Binary Mode. In binary mode, the one's complement of the contents

of DR replace the contents of DR. CY and OVF are cleared.

BCD Mode. In BCD mode, the nine's complement of the contents of

DR replace the contents of DR. CY and OVF are cleared.

Example:

NCB R30

TC

CPU Instruction

Ten's (Or Two's) Complement

Format:

TCB DR

Ten's (or two's) complement byte

TCM DR

Ten's (or two's) complement multi-byte

Operation:

$DR \leftarrow \overline{DR} + 1$

Description: Binary Mode. In binary mode, the two's complement of the contents of DR replaces the contents of DR. CY is set if the contents of DR were zero. OVF is set if contents of DR were 100...000.

> BCD Mode. In BCD mode, the contents of DR are replaced with their ten's complement. CY is set if the contents of DR were zero. OVF is cleared.

Example:

TCM R50

### TEST INSTRUCTION

The test instruction can check the status of single-byte or multi-byte CPU registers.

TS

CPU Instruction

Test

Format:

TSB DR

Test byte

TSM DR

Test multi-byte

Description: The contents of DR are tested and condition flags are set accord-

ingly. CY and OVF are cleared.

Example:

TSM R36

### REGISTER CLEAR INSTRUCTION

The clear instruction permits the clearing of any byte or of any multi-byte portion of the CPU register bank.

CL

CPU Instruction

Clear

Format:

CLB DR

Clear byte

CLM DR

Clear multi-byte

Operation:

$DR \leftarrow 0$

Description: DR is cleared. CY and OVF are cleared.

Example:

CLB R47

### SUBROUTINE JUMP INSTRUCTION

The subroutine jump instruction is available in the literal direct or the indexed addressing mode.

JSB

CPU Instruction

Jump to Subroutine

Format:

JSB = label

Jump subroutine literal direct

JSB XR, label

Jump subroutine indexed

Operation:

<u>Literal Direct</u>. M(SP) ← PC+3, SP ← SP+2, PC ← M(PC+1)

Indexed.  $M(SP) \leftarrow PC+3$ ,  $SP \leftarrow SP+2$ ,  $PC \leftarrow AR + M(PC+1)$

Description:

The PC is saved in the memory location addressed by the R6 stack pointer. Program control is then transferred to the location defined by the label. In indexed addressing, control is transferred to the location defined by the two-byte contents of the address

register plus the label.

After a subroutine jump, the next RTN instruction executed causes a return to the instruction after the JSB.

Examples:

JSB = LOC1

JSB X32, LOC2

Note: Since an indexed subroutine jump (i.e., JSB XR, label) can cause a jump to an unlabeled destination, the programmer must ensure that the ARP and DRP are set to ensure proper operation at the destination. See Handling of ARP and DRP During Assembly later in this section.

### CONDITIONAL JUMP INSTRUCTION

The conditional jump instruction can alter execution based on 16 different conditions in the CPU.

| J                | CPU Instruction |

|------------------|-----------------|

| Conditional Jump |                 |

| Format: | JMP <u>label</u> | Unconditional jump                                                            |

|---------|------------------|-------------------------------------------------------------------------------|

|         | JNO <u>label</u> | Jump on no overflow                                                           |

|         | JOD <u>label</u> | Jump on odd                                                                   |

|         | JEV <u>label</u> | Jump on even                                                                  |

|         | JPS <u>label</u> | Jump on positive Takes overflow into                                          |

|         | JNG <u>label</u> | <pre>Jump on negative } consideration. (Exclu- sive OR of MSB and OVF.)</pre> |

|         | JZR <u>label</u> | Jump on zero                                                                  |

|         | JNZ <u>label</u> | Jump on non-zero                                                              |

|         | JEZ <u>label</u> | Jump on E zero                                                                |

|         | JEN <u>label</u> | Jump on E non-zero                                                            |

|         | JCY <u>label</u> | Jump on carry                                                                 |

|         | JNC <u>label</u> | Jump on no carry                                                              |

|         | JLZ <u>label</u> | Jump on left digit zero                                                       |

|         | JLN <u>label</u> | Jump on left digit non-zero                                                   |

|         | JRZ label        | Jump on right digit zero                                                      |

|         | JRN <u>label</u> | Jump on right digit non-zero                                                  |

|         |                  |                                                                               |

Description: This group of instructions gives the capability of branching as a function of status conditions previously generated. The branching capability uses relative addressing. If the status condition interrogated is found to be true, then the relative branch to the address of the label will be taken. Otherwise, the next instructions after the jump will be executed.

> Each jump instruction is assembled into two bytes: An opcode, and an offset in two's complement notation.

A jump can cover  $400_8$  destinations from  $200_8$  before the next instruction to  $177_8$  after the next instruction. The address to which the jump is made is the sum of the address of the jump instruction plus the offset plus two.

### Example:

JMP INITAL When assembled, this instruction would appear as shown below.

## ARP AND DRP LOAD INSTRUCTIONS

Two instructions are available for loading the address register pointer or the data register pointer. These instructions are not normally needed because the assembler automatically generates necessary ARPs and DRPs where required.

**ARP**

CPU Instruction

Load ARP

Format:

ARP AR

Operation:

ARP

Description: Sets address register pointer to point to address register.

Example:

ARP R25 Sets ARP to point to R25.

DRP

CPU Instruction

Load DRP

Format:

DRP DR

Operation:

DRP

Description: Sets data register pointer to point to data register.

Example:

DRP R25

Sets DRP to R25.

#### NOTE

The instructions to load DRP indirectly with RØ and to load ARP indirectly with RØ are:

DRP 1

ARP 1

Thus, to avoid confusion, R1 is not allowed in either the  $\overline{DR}$  or  $\overline{AR}$  fields. This means that CPU register R1 is for all practical purposes inaccessible except by means of a multi-byte RØ operation or when RØ = 1 and the ARP or DRP is specified by R\*. See Using R\* later in this section.

### OTHER INSTRUCTIONS

In addition to the instructions above, there are a few other instructions which the programmer can use to manipulate quantities in the CPU and memory.

BCD

CPU Instruction

Set Decimal Mode

Format:

DCM

Operation:

DCM + 1

Description: Sets DCM to 1 so that arithmetic operations will be in binary-

coded decimal.

BIN

CPU Instruction

Set Binary Mode

Format:

BIN

Operation:

DCM ← 0

Description: Sets DCM to zero so arithmetic operations performed will be in

binary.

CLE

CPU Instruction

Clear E

Format:

CLE

Operation:  $E \leftarrow 0$

Description: All four bits of the E (extend) register are cleared to zero.

DCE

CPU Instruction

Decrement E

Format:

DCE

Operation:  $E \leftarrow E - 1$

Description: E (extend) register decremented by 1. This instruction is always a binary operation, regardless of the setting of the DCM status

flag.

ICE

CPU Instruction

Increment E

Format:

ICE

Operation:

$E \leftarrow E + 1$

Description: E (extend) register incremented by 1. This instruction is always a binary operation, regardless of the setting of the DCM status flag.

PAD

CPU Instruction

Pop ARP, DRP and Status

Format:

PAD

Operation:

$M(SP) \rightarrow ARP$ , DRP and all status flags except E.

Description:

Restore ARP, DRP and status (usually after a PAD instruction) by popping them off the stack.

Stack pointer is decremented by 3, and all status flags except E are altered by the contents of the three stack locations that are read.

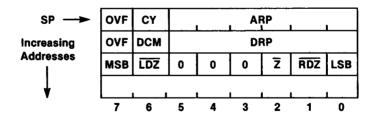

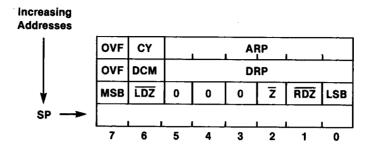

The first byte processed is read as LSB in bit 0,  $\overline{RDZ}$  in bit 1,  $\overline{Z}$  in bit 2,  $\overline{LDZ}$  in bit 6 and MSB in bit 7. The second byte is read as DRP in bits 0-5, DCM status in bit 6, and overflow flags in bit 7. The third byte is read as ARP in bits 0-5, carry flag in bit 6, and overflow flag in bit 7.

Following a PAD instruction, the stack has been read as shown here:

RTN CPU Instruction

Return From Subroutine

Format: RTN

Operation:  $SP \leftarrow SP - 2$ ,  $PC \leftarrow M(SP)$

Description: Subroutine return stack pointer is decremented by two. Then the

return address is read from the stack and written into the program

counter.

SAD CPU Instruction

Save ARP, DRP and Status

Format: SAD

Operation:  $M(SP) \leftarrow ARP$ , and all status flags except E.

Description: Saves ARP, DRP and status (except E) in memory locations addressed

by SP (stack pointer).

Three bytes are pushed onto the stack. The first byte contains ARP in bits 0-5, CY in bit 6, and the overflow flag in bit 7. The second byte contains DRP in bits 0-5, DCM status in bit 6, and the overflow flag in bit 7. The third byte contains LSB in bit 0, RDZ in bit 1,  $\overline{Z}$  in bit 2,  $\overline{LDZ}$  in bit 6, and MSB in bit 7.

SP is then incremented by three. Status is not affected by this operation.

Following a SAD instruction, the stack contents are as shown here:

### USE OF R\*

When entering source code, the programmer may substitute R\* for the AR or DR in any CPU instruction. R\* causes the ARP or DRP to be loaded with the least significant six bits of CPU register R $\emptyset$ . The effect is that the DR and AR are specified by the contents of R $\emptyset$ .

Example: LDB RØ, = 26 Loads RØ with 26.

LDB R\*, R30 Loads CPU register specified by RØ (i.e.,

R26 now) with contents of R30.

STB R40, R\* Stores contents of R40 into register (R26

now) specified by RØ.

### ASSEMBLY OF CPU INSTRUCTIONS

When the address field of an instruction consists of a DR and an AR, each source statement is usually assembled into three bytes of machine code. These bytes are assembled in order as:

1. DRP: DRP set to point to DR.

2. ARP: ARP set to point to AR.

3. Opcode: Perform operation.

Thus, a stack push instruction such as PUBD would be assembled and appear as shown here:

Byte No. Machine Code Source Code

000227 110 006 342 PUBD R10, -R6

When the address field of an instruction consists of a DR and a label, as in the case of literal direct and literal indirect addressing (e.g., LDMI R32, = ADDRS), each source statement is usually assembled into four bytes of machine code:

- 1. DRP: DRP set to point to DR.

- 2. Opcode: Perform operation.

- 3. Low-order byte of literal quantity.

- 4. High-order byte of literal quantity.

When the address field of an instruction consists of DR, AR, and a label, as in the case of indexed direct and indexed indirect addressing (e.g., LDBI R36, X32, TABLE), five bytes of machine code may be generated for each source statement:

- 1. DRP: DRP set to point to DR.

- 2. ARP: ARP set to point to AR.

- 3. Opcode: Perform operation.

- 4. Low-order byte of address.

- 5. High-order byte of address.

#### HANDLING OF ARP AND DRP DURING ASSEMBLY

An optimizing feature of the Assembler ROM is the deletion of "unnecessary" ARP and DRP instructions during assembly.

If an instruction is not labeled (i.e., there is not an entry in the label field) and the ARP (and/or DRP) is already set to the correct value, the previously-set ARP (and/or DRP) is not generated during assembly.

#### For example:

|     | Code | ource | So    | Code | hine | Mac | Byte No. |

|-----|------|-------|-------|------|------|-----|----------|

| -R6 | R10, | POBD  | LABEL | 342  | 006  | 110 | 000227   |

| -R6 | R10, | POBD  |       |      |      | 342 | 000232   |

In this example, both the ARP and the DRP are specified beginning with byte 227. Since they are now correctly set for the next instruction, they are automatically deleted when the second POBD R10, -R6 instruction is assembled. This results in the machine code shown in byte 232.

Not all previously-set ARPs and DRPs are deleted during assembly. Instances where a previously-set ARP and/or DRP will not be deleted include:

--<u>Labeled instructions</u>. Since a jump from anyplace in code may cause execution to resume at the label, the first ARP and DRP are not deleted after an instruction that contains an entry in the label field.

- --Returns. After executing a JSB, then returning, the first ARP and DRP encountered are not deleted.

- -- PAD. Following a PAD instruction, the first ARP and DRP are not deleted.

#### USING R#

When entering CPU instructions, the user may substitute R# in almost any instruction requiring an AR or DR. R# causes the ARP or DRP to be deleted from the machine code, regardless of other conditions. For example:

| Byte No. | Machine Code | Source Code      |  |  |

|----------|--------------|------------------|--|--|

| 000265   | 240          | LABEL LDB R#, R# |  |  |

R# is normally used after labels, when the ARP and DRP are already set correctly. By using R#, it is not necessary to squander time or bytes resetting ARP and DRP.

### PSEUDO-INSTRUCTIONS

Pseudo-instructions are instructions to the assembler. Each may be entered by typing a pseudo-opcode in the same field as the opcode for an instruction, followed by any additional required operand.

Pseudo-instructions perform three main functions when encountered during assembly:

- --Assembly control

- --Data definition

- --Conditional Assembly

### PSEUDO-INSTRUCTIONS FOR ASSEMBLY CONTROL

ABS

Pseudo-Instruction

Absolute Program

Format:

**ABS 16**

ABS 32

ABS ROM base address

Description: Declares an absolute program (i.e., with addresses that cannot be relocated), for either a computer with 16K bytes of memory, a computer with 32K bytes, or for a ROM beginning with the specified base address. If ABS 16 or ABS 32 is declared, the instruction must precede a NAM instruction.

FIN

Pseudo-Instruction

Finish Program

Format:

FIN

Description: Signifies the end of the source code. This pseudo-instruction is

required for assembly.

GIO

Pseudo-Instruction

Declare Global File

Format:

GLO

GLO file name

Description: If no file name, declares this source code to be a global file. Otherwise, declares the global file to be used in the assembling of the current source code. Comments are not allowed on the same line as the GLO instruction, and the instruction must precede ABS and

NAM.

INK

Pseudo-Instruction

Link Files At Assembly

Format:

LNK file name

Description: Will load another file containing more source code and continue assembling. Allows assembly of larger programs than would otherwise be possible.

Example:

LNK SOURC2 When this instruction is encountered during assembly, the assembler looks for the file SOURC2 on the current mass storage device, loads the file, and continues assembling using the source code from the file.

IST List Pseudo-Instruction

Format:

LST

Description: Causes the code to be listed on the current PRINTER IS device at assembly time. If the column width of the printer is sufficient (>46 characters) the listing will contain both the object and source code; otherwise, only the object code will be listed.

> An address that is undefined when its label is encountered will be printed in object code as 326, 336, or 377, depending upon whether it is a DEF, a relative jump, or a GTO statement.

MAM

Pseudo-Instruction

Name Program

Format:

NAM unquoted string

Description: Sets up the PCB (Program Control Block) for a binary program.

Should be preceded only by GLO, ABS, LST, UNL, DAD, EQU, or com-

ments. Illegal when ABS ROM has been declared.

Example:

NAM KEYHIT Names a binary program KEYHIT and sets up the  $32_{o}$ -byte

program control block for that program.

ORG

Pseudo-Instruction

**Origin**

Format:

ORG address

Description:

Specifies a base address which is added to all following defined

addresses (DAD's). This pseudo-instruction is most useful in global

files.

UNI

Pseudo-Instruction

Unlist

Format:

UNL

Description: Turns off the list feature which was turned on by the LST pseudo-

instruction. After an UNL, code is not listed during assembly.

### PSEUDO-INSTRUCTIONS FOR DATA DEFINITION

ASC

Pseudo-Instruction

ASCII

Format:

ASC numeric value, unquoted string

ASC quoted string

Description: Inserts into the object code the ASCII code for the number of characters specified of the unquoted string. Inserts the entire quoted

string.

Example:

ASC 3, FTOC Inserts the ASCII code for FTO.

ASC 4, FTOC Inserts the ASCII code for FTOC.

ASC "LOCATION" Inserts the ASCII code for LOCATION.

**ASP**

Pseudo-Instruction

**ASCII** With Parity

Format:

ASP numeric value, unquoted string

ASP quoted string

Description: Same as ASC except that the parity bit (MSB) of the string's final character is set. (During operation, the HP-83/85 system determines the end of an ASCII string in some system tables by checking to see if the character's parity bit is set. When the bit is found set, the system assumes the next character begins a new string or entry

in the table.)

**BSZ**

Pseudo-Instruction

Bytes To Zero

Format:

BSZ numeric value

Description: Inserts into the object code the octal number of bytes of zeros

specified by the numeric value.

Example:

BSZ 30 Fills  $30_{\rm R}$  bytes with zeros.

**BYT**

Pseudo-Instruction

Bytes To Values

Format:

BYT numeric value [,numeric value...]

Description: Inserts literal values into the object code.

Examples:

Inserts octal 377 (i.e., all ones) into object code. BYT 377

Inserts octal 20 into this byte of object code and BYT 20.55C

BCD 55 into next byte.

DAD

Pseudo-Instruction

Direct Address

Format:

Label DAD address

Description: Assigns either an absolute address or a constant to a label. and EQU are similar; DAD is usually used for addresses, while EQU is used for values other than addresses. ORG affects only DAD's.

Example:

Assigns absolute address 56343 to the label INTORL DAD 56343

INTORL.

DEF Pseudo-Instruction

Define Label Address

Format: DEF <u>label</u>

Description: Inserts the two-byte address associated with the label.

Example: DEF RUNTIM Inserts two-byte address of the label RUNTIM.

EQU Pseudo-Instruction

Equals

Format: <u>Label EQU numeric value</u>

Description: Assigns either an absolute address or a constant to a label. DAD

and EQU are similar; DAD is usually used for addresses, while EQU

is used for values other than addresses. ORG affects only DAD's.

GT0 Go To Pseudo-Instruction

Format:

GTO label

Description:

Generates four bytes of object code which load the program counter (CPU registers 4 and 5) with the address minus one (i.e., ADR-1) of the label. The label must be for an absolute address.

The CPU relative jump instructions (JRZ, JNO, etc.) can cause jumps of from 177 $_8$  to -200 $_8$  memory locations. The GTO pseudo-instruction is useful for jumping beyond the range of relative jumps.

### WARNING

The GTO pseudo-instruction is primarily for use in ROMs. It should not be used in a binary program unless that program has been declared an absolute program.

Example:

GTO INTORL

VAI

Pseudo-Instruction

Value

Format:

VAL label

Description: Inserts the one-byte literal octal value associated with the label.

Example:

PPROM# EQU 360

Inserts the one-byte literal octal value (360) of the VAL PPROM#

label PPROM# into the object code.

PSEUDO-INSTRUCTIONS FOR CONDITIONAL ASSEMBLY

This set of pseudo-instructions permits the user to control assembly by means of conditional assembly flags. A conditional assembly flag has the same constraints as a label--it can be no more than six characters in length, and the first character cannot be a digit.

A conditional assembly flag is treated the same as a label by the HP-83/85 system. (For example, an assembly flag can be located by a label search.) For this reason, a conditional assembly flag name should be unique, and should not duplicate a label.

AIF Pseudo-Instruction

Assemble If Flag True

Format: AIF <u>assembly flag name</u>

Description: Tests the specified conditional assembly flag and, if true, con-

tinues to assemble the following code. If the flag tests false, the source code after the flag is treated as if it were a series

of comments until an EIF instruction is found.

Example: AIF CYCLE Tests assembly flag CYCLE.

CLR Pseudo-Instruction

Clear Flag

Format: CLR <u>flag name</u>

Description: Clears the specified conditional assembly flag to the false state.

Example: CLR CYCLE Clears assembly flag CYCLE.

EIF

Pseudo-Instruction

End Of Conditional Assembly

Format:

EIF

Description: Terminates any conditional assembly in process. Only one conditional assembly can be handled at a time. If a second one is encountered while the first is still active, the second will

override the first.

SET

Pseudo-Instruction

Set Flag

Format:

SET flag name

Description: Sets the specified conditional assembly flag to the true state.

Example:

SET CYCLE Sets conditional assembly flag CYCLE.

### APPENDIX C

#### ASSEMBLER INSTRUCTION SET

On the following pages is a list of all CPU instructions available on the Assembler ROM.

**LEGEND**

DR Data register. Can be register number (e.g., R32), R\* or R#.

AR Address register. Can be register number (e.g., R32), R\* or

R#.

<u>Literal</u> Literal value, up to  $10_8$  bytes in length. Can be BCD constant

(e.g., 99C), octal constant (e.g., 12), or decimal constant (e.g., 20D). Can also be specified by a label, where the literal quantity is a one- or two-byte value or address

assigned to the label.

Label Address of literal quantity. Label name must begin with an

alphabetic character, can use any combination of alphanumeric

characters, and can be 1-6 characters in length.

Clock Cycle 1.6 µsec.

B Number of bytes.

Add one clock cycle if true (i.e., the jump occurs).

R(x) CPU register addressed by (x).

M(x) Memory location addressed by (x). (x) must be a 16-bit

address.

PC Program Counter. CPU registers R4 and R5. Used to address

the instruction being executed.

## Assembler Instruction Set

| SP          | Subroutine Stack Pointer. CPU registers R6 and R7. Used to point to the next available location on the subroutine return address stack.                                                              |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EA          | Effective Address. The location from which data is read for load-type instructions or the location where data is placed for store-type instructions.                                                 |

| ADR         | Address. The two-byte quantity directly following an instruction that uses the literal direct, literal indirect, index direct or index indirect addressing mode. This quantity is always an address. |

| n           | Literal value.                                                                                                                                                                                       |

| <b>←</b>    | Is transferred to.                                                                                                                                                                                   |

| ( )         | Contents of.                                                                                                                                                                                         |

| <del></del> | Complement (e.g., $\overline{x}$ is complement of x). This is one's complement if DCM=0 and nine's complement if DCM=1.                                                                              |

| •           | Logical AND.                                                                                                                                                                                         |

| ٧           | Inclusive OR.                                                                                                                                                                                        |

| $\oplus$    | Exclusive OR.                                                                                                                                                                                        |

| JIF         | Jump if.                                                                                                                                                                                             |

| 1           | Status bit is set.                                                                                                                                                                                   |

| Ø           | Status bit is cleared.                                                                                                                                                                               |

| X           | Status bit is affected.                                                                                                                                                                              |

- Status bit is not affected.

- Y This option is available to this instruction.

The complete list of CPU instructions begins on the next page.

|                                      |                             | •                  |                                |                 |               |     |     |            |          | St   | atus     | 5    |     |   |     | -         | Binary/       |

|--------------------------------------|-----------------------------|--------------------|--------------------------------|-----------------|---------------|-----|-----|------------|----------|------|----------|------|-----|---|-----|-----------|---------------|

| Instruction<br>Format                | Description                 | Addressing<br>Mode | OpCode                         | Clock<br>Cycles | Operation     | LSR | MSR | RDZ        | 7        | DCM. | ,        | DCM: | OVF | F | DCM | =1<br>OVF | BCD<br>Option |

| ADB DR, AR                           | Add byte                    | Reg. imm.          | 302                            | 5               | DR+DR+AR      | Х   | Х   | X          | <u> </u> | -    | <u>-</u> | х    | х   |   | х   | 0         | Υ             |

| ADB <u>DR</u> , =<br>literal         | Add byte                    | Lit. imm.          | 312                            | 5               | DR+DR+M(PC+1) |     | х   | х          | Х        | -    | -        | х    | x   |   | х   | 0         | Y             |

| ADBD <u>DR</u> , <u>AR</u>           | Add byte                    | Reg. dir.          | 332                            | 6               | DR+DR+M(AR)   | х   | X   | χ.         | X        | -    | -        | X    | X   | - | X   | 0         | Υ             |

| ADBD <u>DR</u> , =<br><u>label</u>   | Add byte                    | Lit. dir.          | 322                            | 5               | DR←DR+M(ADR)  | Х   | X   | X          | X        | -    | -        | X    | X   | - | X   | 0         | Y             |

| ADM <u>DR</u> , <u>AR</u>            | Add multi-<br>byte          | Reg. imm.          | 303                            | 4+B             | DR+DR+AR      | Χ.  | X   | X          | x        | -    | -        | X    | X   | - | X   | 0         | Y             |

| ADM <u>DR</u> , =<br>literal         | Add multi-<br>byte          | Lit. imm.          | 313                            | 4+B             | DR+DR+M(PC+1) | х   | X   | x          | x        | -    | -        | X    | X   | - | X   | 0         | Y             |

| ADMD <u>DR</u> , <u>AR</u>           | Add multi-<br>byte          | Reg. dir.          | 333                            | 5+B             | DR←DR+M(AR)   | х   | X   | X          | X        | -    | -        | X    | X   | - | X   | 0         | Y             |

| ADMD <u>DR</u> , =<br><u>label</u>   | Add multi-<br>byte          | Lit. dir.          | 323                            | 4+B             | DR←DR+M(ADR)  | х   | X   | X          | X        | -    | -        | X    | Х   | - | X   | 0         | Y             |

| ANM <u>DR</u> . <u>AR</u>            | Logical AND<br>(multi-byte) | Reg. imm.          | 307                            | 4+B             | DR←DR∙AR      | х   | X   | X          | X        | -    | -        | 0    | 0   | - | 0   | 0         |               |

| ANM <u>DR</u> , =<br>literal         | Logical AND<br>(multi-byte) | Lit. imm.          | 317                            | 4+B             | DR+DR·M(PC+1) | х   | x   | X          | X        | -    | -        | 0    | 0   | - | 0   | 0         |               |

| ANMD <u>DR</u> , <u>AR</u>           | Logical AND<br>(multi-byte) | Reg. Dir.          | 337                            | 5+B             | DR←DR·M(AR)   | x   | x   | X          | X        | -    | -        | 0    | 0   | - | 0   | 0         |               |

| ANMD <u>DR</u> , =<br><u>literal</u> | Logical AND<br>(multi-byte) | Lit. dir.          | 327                            | 5+B             | DR←DR•M(ADR)  | х   | ×   | X          | X        | -    | -        | 0    | 0   | - | 0   | 0         |               |

| ARP <u>AR</u>                        | Load ARP                    |                    | 000-077<br>( <del>/</del> 001) | 2               | ARP←n         | -   | -   | <b>-</b> . | -        | -    | -        | -    | -   | - | -   | -         |               |

| ARP *                                | Load ARP with contents      |                    | 001                            | 3               | ARP←RØ        | -   | -   | -          | -        | -    | -        | -    | -   | - | -   | -         |               |

| BCD                                  | Set BCD mode                |                    | 231                            | 4               | DCM←1         | -   | -   | -          | -        | 1    | -        | -    | -   | - | -   | -         |               |

| BIN                                  | Set binary<br>mode          |                    | 230                            | 4               | DCM+0         | -   | -   | -          | -        | 0    | -        | -    | -   | - | -   | -         |               |

| CLB <u>DR</u>                        | Clear byte                  | Reg. imm.          | 222                            | 5               | DR <b>←</b> 0 | Х   | X   | X          | X        | -    | -        | 0    | 0   | - | 0   | 0         |               |

| CLM <u>DR</u>                        | Clear multi-<br>byte        | Reg. imm.          | 223                            | 4+B             | DR+O          | х   | X   | X          | X        | -    | -        | 0    | 0   | - | 0   | 0         |               |

| CLE                                  | Clear E                     |                    | 235                            | 2               | E+0           | -   | -   | -          | -        | -    | 0        | -    | -   | 0 | -   | -         |               |